DS33Z41 Quad IMUX Ethernet Mapper

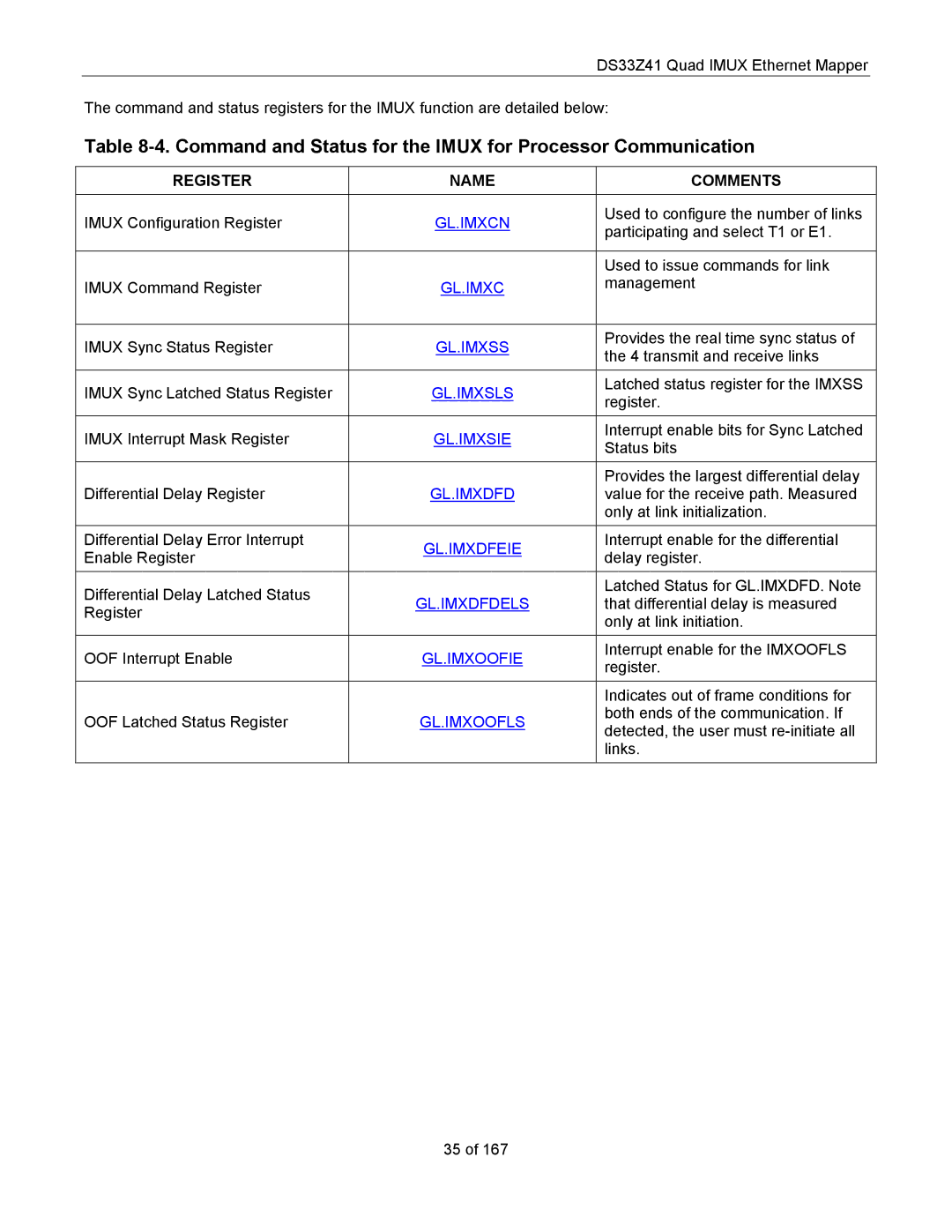

The command and status registers for the IMUX function are detailed below:

Table 8-4. Command and Status for the IMUX for Processor Communication

REGISTER | NAME | COMMENTS | |

|

|

| |

IMUX Configuration Register | GL.IMXCN | Used to configure the number of links | |

participating and select T1 or E1. | |||

|

| ||

|

|

| |

|

| Used to issue commands for link | |

IMUX Command Register | GL.IMXC | management | |

|

|

| |

IMUX Sync Status Register | GL.IMXSS | Provides the real time sync status of | |

the 4 transmit and receive links | |||

|

| ||

|

|

| |

IMUX Sync Latched Status Register | GL.IMXSLS | Latched status register for the IMXSS | |

register. | |||

|

| ||

IMUX Interrupt Mask Register | GL.IMXSIE | Interrupt enable bits for Sync Latched | |

Status bits | |||

|

| ||

|

|

| |

Differential Delay Register | GL.IMXDFD | Provides the largest differential delay | |

value for the receive path. Measured | |||

|

| only at link initialization. | |

Differential Delay Error Interrupt | GL.IMXDFEIE | Interrupt enable for the differential | |

Enable Register | delay register. | ||

| |||

|

|

| |

Differential Delay Latched Status | GL.IMXDFDELS | Latched Status for GL.IMXDFD. Note | |

that differential delay is measured | |||

Register | |||

| only at link initiation. | ||

|

| ||

|

|

| |

OOF Interrupt Enable | GL.IMXOOFIE | Interrupt enable for the IMXOOFLS | |

register. | |||

|

| ||

|

|

| |

|

| Indicates out of frame conditions for | |

OOF Latched Status Register | GL.IMXOOFLS | both ends of the communication. If | |

detected, the user must | |||

|

| ||

|

| links. | |

|

|

|

35 of 167