DS33Z41 Quad IMUX Ethernet Mapper | |

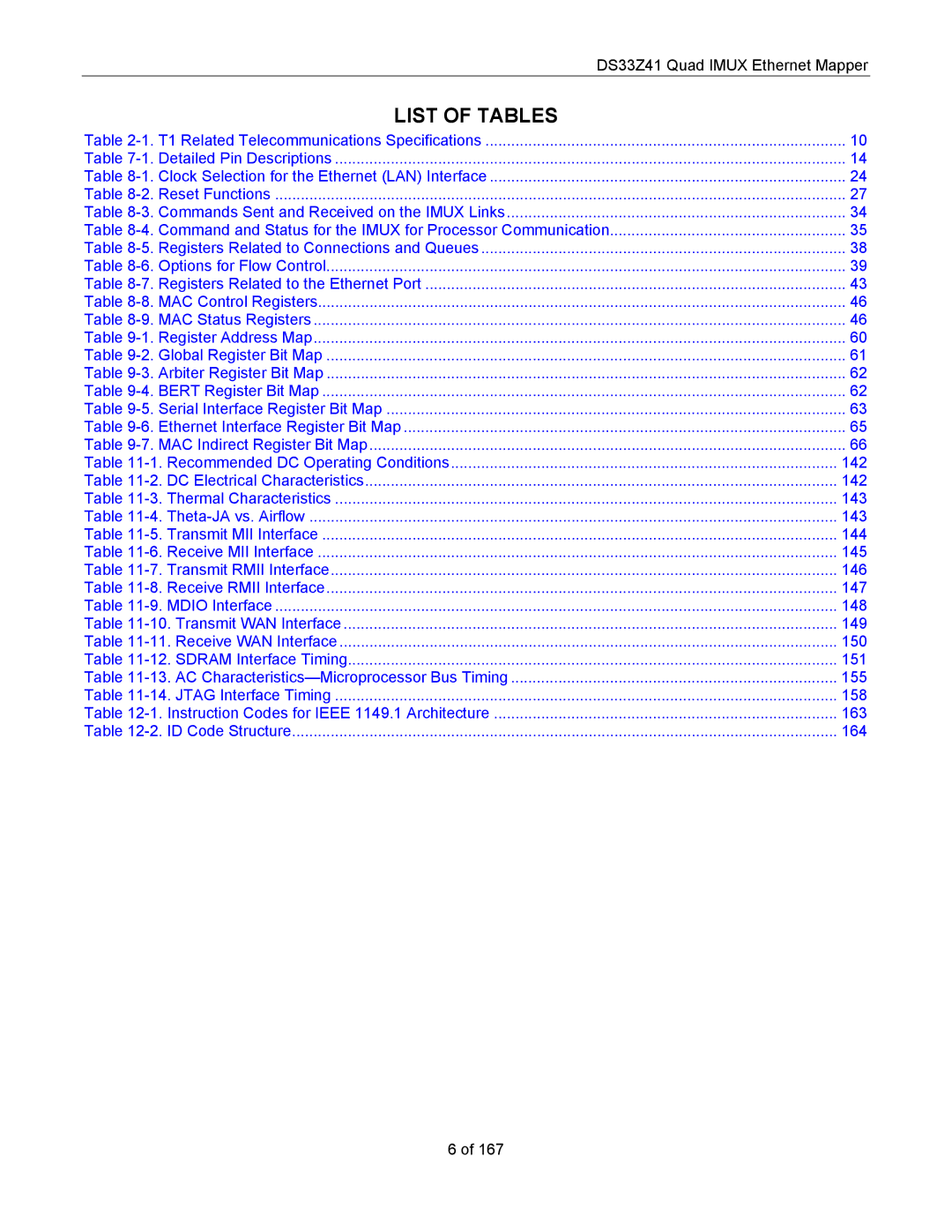

LIST OF TABLES |

|

Table | 10 |

Table | 14 |

Table | 24 |

Table | 27 |

Table | 34 |

Table | 35 |

Table | 38 |

Table | 39 |

Table | 43 |

Table | 46 |

Table | 46 |

Table | 60 |

Table | 61 |

Table | 62 |

Table | 62 |

Table | 63 |

Table | 65 |

Table | 66 |

Table | 142 |

Table | 142 |

Table | 143 |

Table | 143 |

Table | 144 |

Table | 145 |

Table | 146 |

Table | 147 |

Table | 148 |

Table | 149 |

Table | 150 |

Table | 151 |

Table | 155 |

Table | 158 |

Table | 163 |

Table | 164 |

6 of 167