DS33Z41 Quad IMUX Ethernet Mapper

8.15.2 Receive Data Interface

8.15.2.1 Receive Pattern Detection

The Receive BERT receives only the payload data and synchronizes the receive pattern generator to the incoming pattern. The receive pattern generator is a

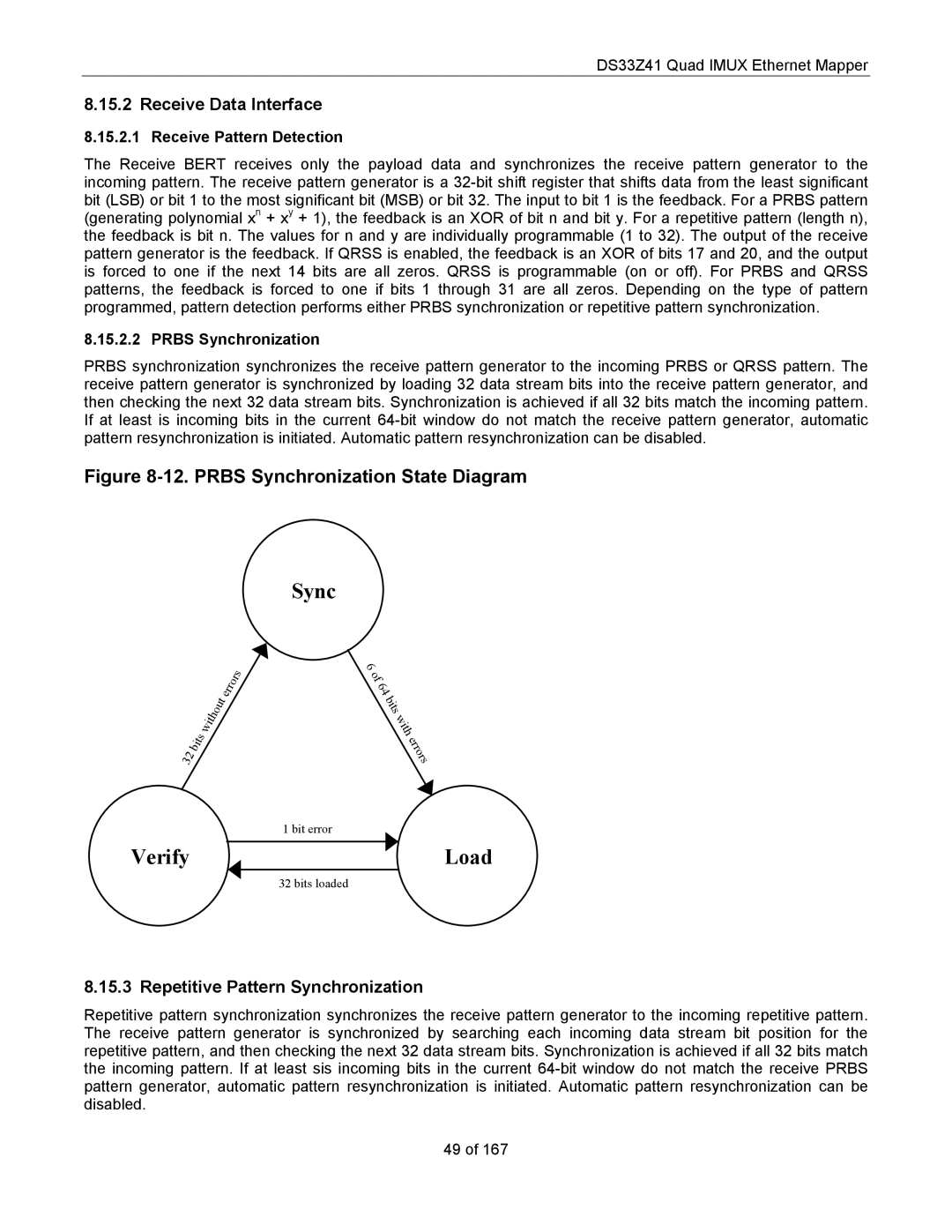

8.15.2.2 PRBS Synchronization

PRBS synchronization synchronizes the receive pattern generator to the incoming PRBS or QRSS pattern. The receive pattern generator is synchronized by loading 32 data stream bits into the receive pattern generator, and then checking the next 32 data stream bits. Synchronization is achieved if all 32 bits match the incoming pattern. If at least is incoming bits in the current

Figure 8-12. PRBS Synchronization State Diagram

Sync

|

|

|

|

|

|

|

|

|

|

|

| r | o | r | s |

|

|

|

|

|

|

|

|

|

|

| r |

| |||

|

|

|

|

|

|

|

|

| t | e |

|

| |||

|

|

|

|

|

|

|

| u |

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

| o |

|

|

|

|

|

| ||

|

|

|

|

| it | h |

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

| w |

|

|

|

|

|

|

|

|

| ||

|

|

| it s |

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| 2 | b |

|

|

|

|

|

|

|

|

|

|

|

| |

3 |

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6

o f

6 4

b i t s

w

i t h

e r r o r s

1 bit error

VerifyLoad

32 bits loaded

8.15.3 Repetitive Pattern Synchronization

Repetitive pattern synchronization synchronizes the receive pattern generator to the incoming repetitive pattern. The receive pattern generator is synchronized by searching each incoming data stream bit position for the repetitive pattern, and then checking the next 32 data stream bits. Synchronization is achieved if all 32 bits match the incoming pattern. If at least sis incoming bits in the current

49 of 167