DS33Z41 Quad IMUX Ethernet Mapper

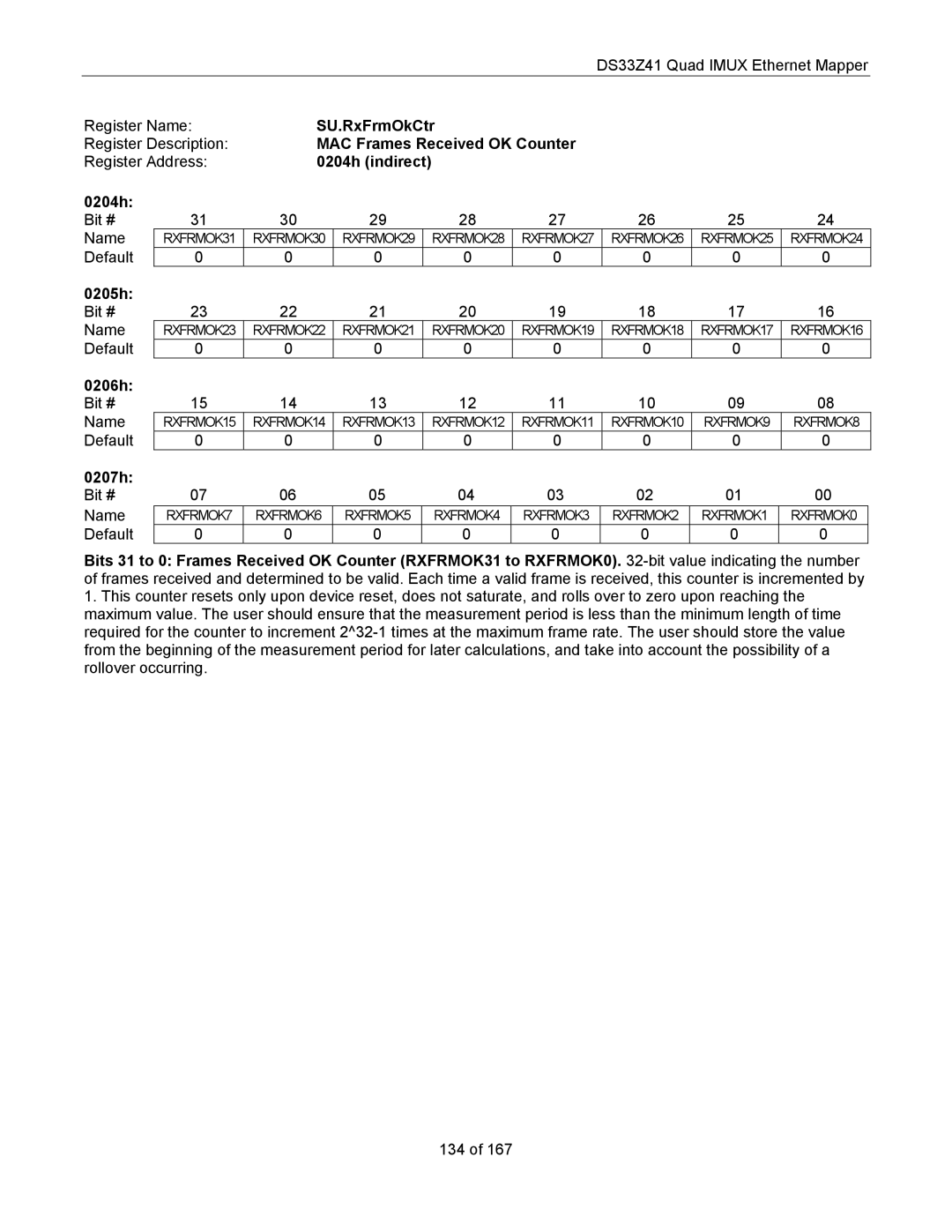

Register Name: | SU.RxFrmOkCtr |

|

|

|

|

| |||||

Register Description: | MAC Frames Received OK Counter |

|

|

|

| ||||||

Register Address: | 0204h (indirect) |

|

|

|

|

|

| ||||

0204h: |

|

|

|

|

|

|

|

|

|

|

|

Bit # | 31 | 30 | 29 |

|

| 28 | 27 | 26 | 25 | 24 |

|

Name | RXFRMOK31 | RXFRMOK30 | RXFRMOK29 |

| RXFRMOK28 | RXFRMOK27 | RXFRMOK26 | RXFRMOK25 | RXFRMOK24 | ||

Default | 0 | 0 | 0 |

|

| 0 | 0 | 0 | 0 | 0 |

|

0205h: |

|

|

|

|

|

|

|

|

|

|

|

Bit # | 23 | 22 | 21 |

|

| 20 | 19 | 18 | 17 | 16 |

|

Name | RXFRMOK23 | RXFRMOK22 | RXFRMOK21 |

| RXFRMOK20 | RXFRMOK19 | RXFRMOK18 | RXFRMOK17 | RXFRMOK16 | ||

Default | 0 | 0 | 0 |

|

| 0 | 0 | 0 | 0 | 0 |

|

0206h: |

|

|

|

|

|

|

|

|

|

|

|

Bit # | 15 | 14 | 13 |

|

| 12 | 11 | 10 | 09 | 08 |

|

Name | RXFRMOK15 | RXFRMOK14 | RXFRMOK13 |

| RXFRMOK12 | RXFRMOK11 | RXFRMOK10 | RXFRMOK9 | RXFRMOK8 | ||

Default | 0 | 0 | 0 |

|

| 0 | 0 | 0 | 0 | 0 |

|

0207h: |

|

|

|

|

|

|

|

|

|

|

|

Bit # | 07 | 06 | 05 |

|

| 04 | 03 | 02 | 01 | 00 |

|

Name | RXFRMOK7 | RXFRMOK6 | RXFRMOK5 |

| RXFRMOK4 | RXFRMOK3 | RXFRMOK2 | RXFRMOK1 | RXFRMOK0 |

| |

Default | 0 | 0 | 0 |

|

| 0 | 0 | 0 | 0 | 0 |

|

Bits 31 to 0: Frames Received OK Counter (RXFRMOK31 to RXFRMOK0).

1.This counter resets only upon device reset, does not saturate, and rolls over to zero upon reaching the maximum value. The user should ensure that the measurement period is less than the minimum length of time required for the counter to increment

134 of 167