DS33Z41 Quad IMUX Ethernet Mapper

Register Name: |

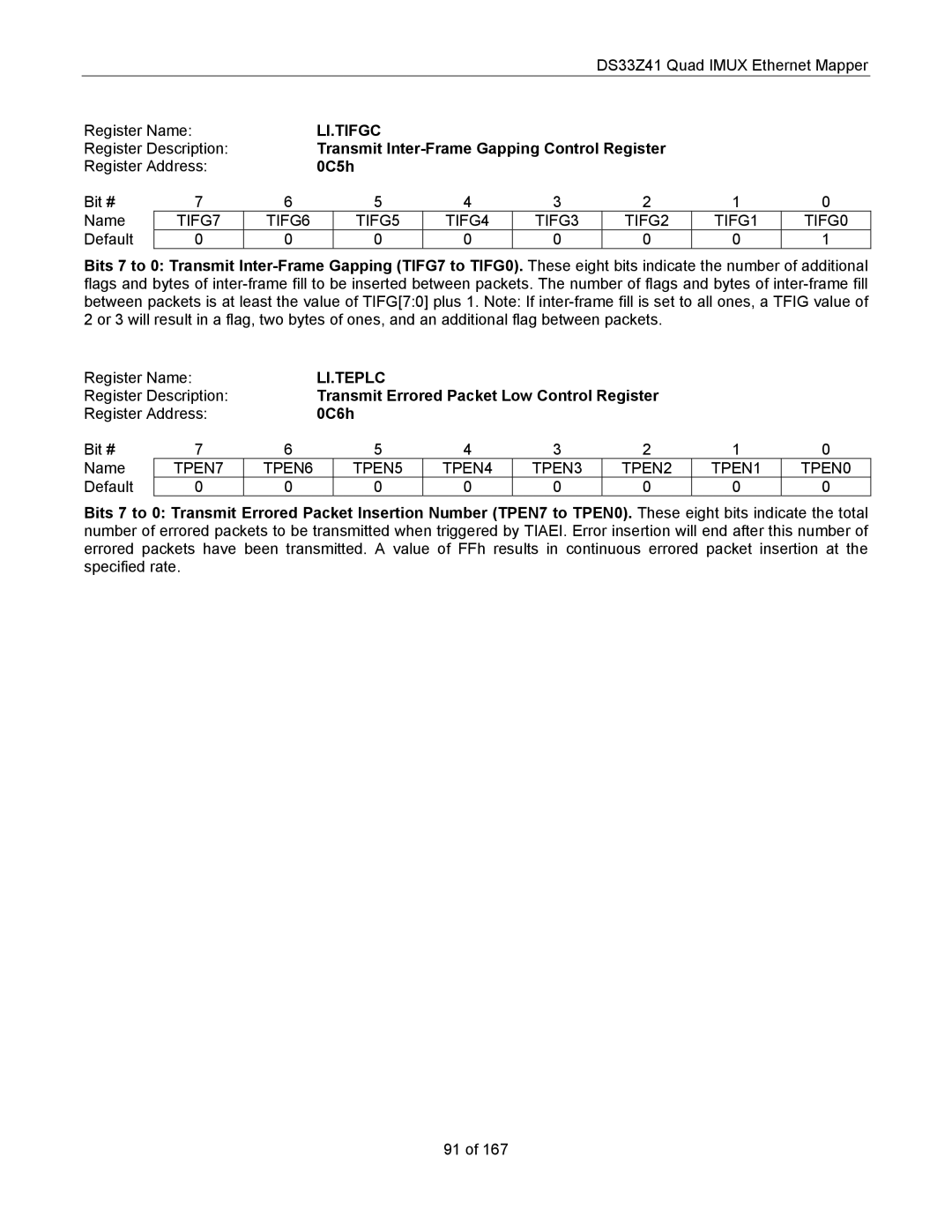

| LI.TIFGC |

|

|

|

|

| ||

Register Description: |

| Transmit |

|

| |||||

Register Address: |

| 0C5h |

|

|

|

|

| ||

Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

Name | TIFG7 | TIFG6 |

| TIFG5 | TIFG4 | TIFG3 | TIFG2 | TIFG1 | TIFG0 |

Default | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 1 |

Bits 7 to 0: Transmit

Register Name: |

| LI.TEPLC |

|

|

|

|

| ||

Register Description: |

| Transmit Errored Packet Low Control Register |

|

| |||||

Register Address: |

| 0C6h |

|

|

|

|

| ||

Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

Name | TPEN7 | TPEN6 |

| TPEN5 | TPEN4 | TPEN3 | TPEN2 | TPEN1 | TPEN0 |

Default | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 |

Bits 7 to 0: Transmit Errored Packet Insertion Number (TPEN7 to TPEN0). These eight bits indicate the total number of errored packets to be transmitted when triggered by TIAEI. Error insertion will end after this number of errored packets have been transmitted. A value of FFh results in continuous errored packet insertion at the specified rate.

91 of 167