DS33Z41 Quad IMUX Ethernet Mapper

12 JTAG INFORMATION

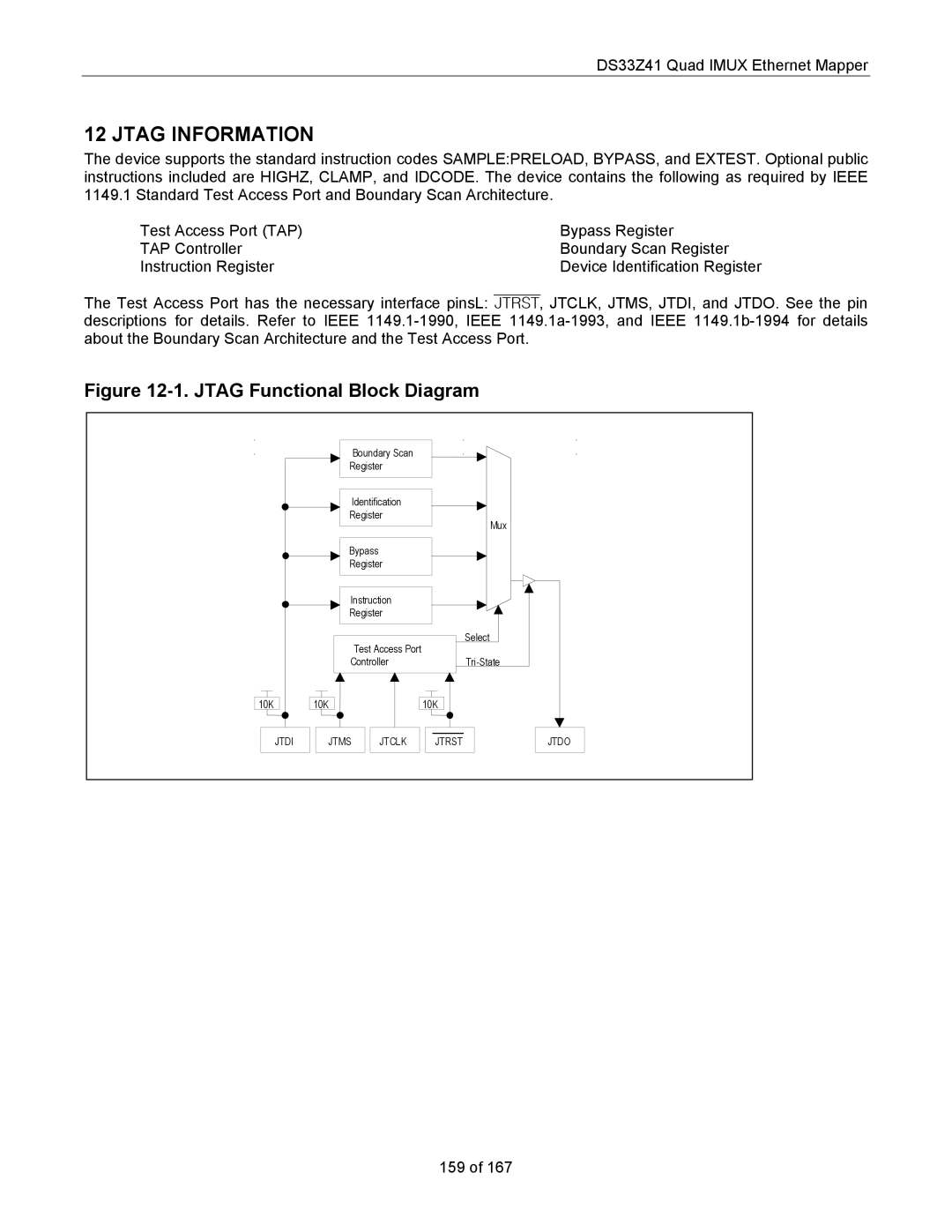

The device supports the standard instruction codes SAMPLE:PRELOAD, BYPASS, and EXTEST. Optional public instructions included are HIGHZ, CLAMP, and IDCODE. The device contains the following as required by IEEE 1149.1 Standard Test Access Port and Boundary Scan Architecture.

Test Access Port (TAP) | Bypass Register |

TAP Controller | Boundary Scan Register |

Instruction Register | Device Identification Register |

The Test Access Port has the necessary interface pinsL: JTRST, JTCLK, JTMS, JTDI, and JTDO. See the pin descriptions for details. Refer to IEEE

Figure 12-1. JTAG Functional Block Diagram

Boundary Scan Register

Identification

Register

Bypass

Register

Instruction

Register

Test Access Port Controller

Mux

Select

10K

10K

10K

JTDI

JTMS

JTCLK

JTRST

JTDO

159 of 167