DS33Z41 Quad IMUX Ethernet Mapper

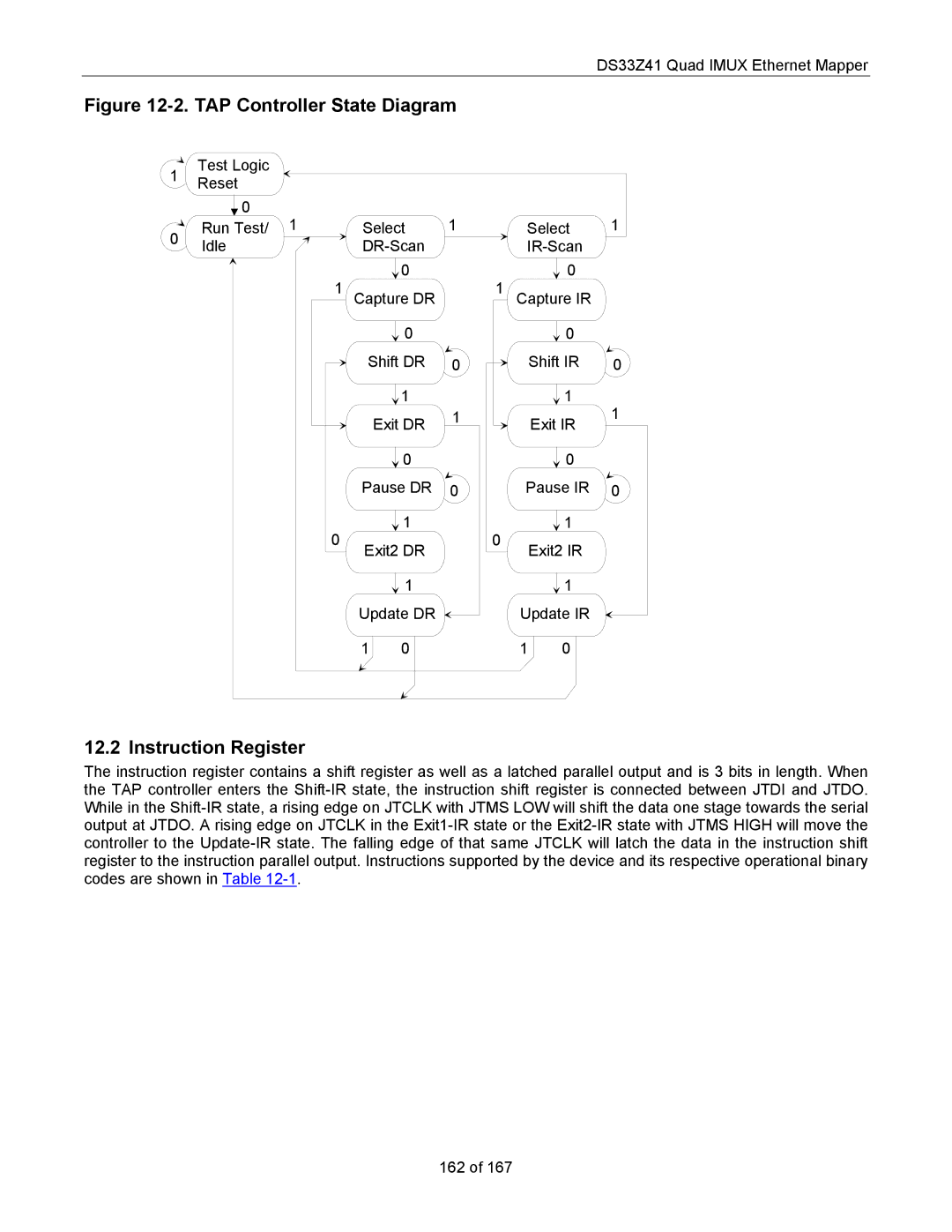

Figure 12-2. TAP Controller State Diagram

1 | Test Logic |

|

|

|

|

|

|

Reset |

|

|

|

|

|

| |

|

|

|

|

|

|

| |

| 0 | 1 |

| 1 |

|

| 1 |

0 | Run Test/ | Select |

| Select | |||

Idle |

|

|

|

| |||

|

|

|

|

| |||

|

| 1 | 0 |

| 1 | 0 |

|

|

| Capture DR |

| Capture IR |

|

|

| 0 |

|

| 0 |

|

| Shift DR | 0 |

| Shift IR | 0 | |

|

| 1 |

|

| 1 | 1 |

|

| Exit DR | 1 |

| Exit IR | |

|

|

|

|

| ||

|

| 0 |

|

| 0 |

|

| Pause DR | 0 | Pause IR | 0 | ||

0 |

| 1 |

| 0 | 1 |

|

Exit2 DR |

| Exit2 IR |

| |||

|

|

|

| |||

|

| 1 |

|

| 1 |

|

| Update DR |

| Update IR |

| ||

| 1 | 0 |

| 1 | 0 |

|

12.2 Instruction Register

The instruction register contains a shift register as well as a latched parallel output and is 3 bits in length. When the TAP controller enters the

162 of 167