DS33Z41 Quad IMUX Ethernet Mapper

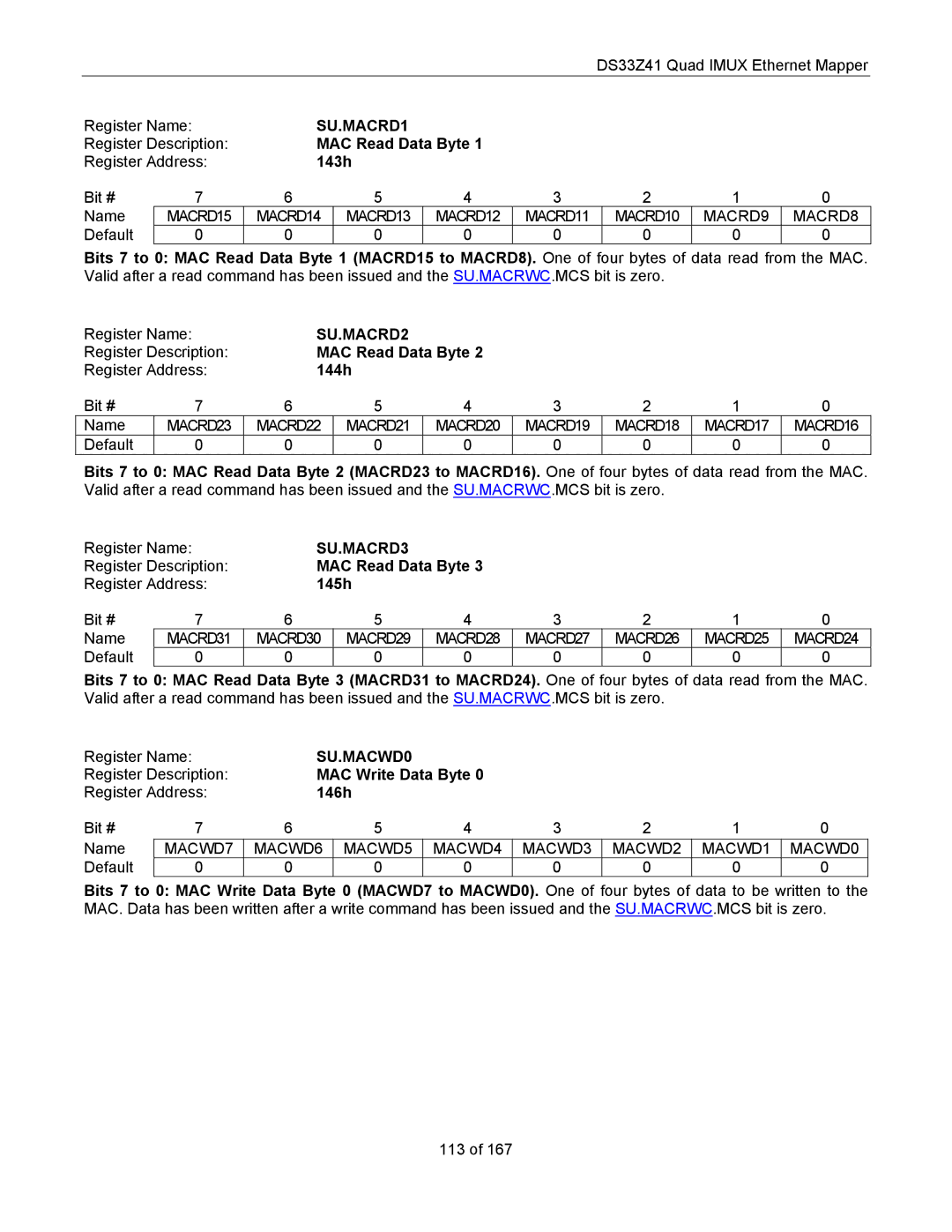

Register Name: | SU.MACRD1 |

|

|

|

|

| ||

Register Description: | MAC Read Data Byte 1 |

|

|

|

| |||

Register Address: | 143h |

|

|

|

|

| ||

Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

Name | MACRD15 | MACRD14 | MACRD13 | MACRD12 | MACRD11 | MACRD10 | MACRD9 | MACRD8 |

Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Bits 7 to 0: MAC Read Data Byte 1 (MACRD15 to MACRD8). One of four bytes of data read from the MAC. Valid after a read command has been issued and the SU.MACRWC.MCS bit is zero.

Register Name: | SU.MACRD2 |

|

|

|

|

| ||

Register Description: | MAC Read Data Byte 2 |

|

|

|

| |||

Register Address: | 144h |

|

|

|

|

| ||

Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

Name | MACRD23 | MACRD22 | MACRD21 | MACRD20 | MACRD19 | MACRD18 | MACRD17 | MACRD16 |

Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Bits 7 to 0: MAC Read Data Byte 2 (MACRD23 to MACRD16). One of four bytes of data read from the MAC. Valid after a read command has been issued and the SU.MACRWC.MCS bit is zero.

Register Name: | SU.MACRD3 |

|

|

|

|

| ||

Register Description: | MAC Read Data Byte 3 |

|

|

|

| |||

Register Address: | 145h |

|

|

|

|

| ||

Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

Name | MACRD31 | MACRD30 | MACRD29 | MACRD28 | MACRD27 | MACRD26 | MACRD25 | MACRD24 |

Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Bits 7 to 0: MAC Read Data Byte 3 (MACRD31 to MACRD24). One of four bytes of data read from the MAC. Valid after a read command has been issued and the SU.MACRWC.MCS bit is zero.

Register Name: | SU.MACWD0 |

|

|

|

|

| ||

Register Description: | MAC Write Data Byte 0 |

|

|

|

| |||

Register Address: | 146h |

|

|

|

|

| ||

Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

Name | MACWD7 | MACWD6 | MACWD5 | MACWD4 | MACWD3 | MACWD2 | MACWD1 | MACWD0 |

Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Bits 7 to 0: MAC Write Data Byte 0 (MACWD7 to MACWD0). One of four bytes of data to be written to the MAC. Data has been written after a write command has been issued and the SU.MACRWC.MCS bit is zero.

113 of 167