DS33Z41 Quad IMUX Ethernet Mapper

9.5.5Receive Serial Interface

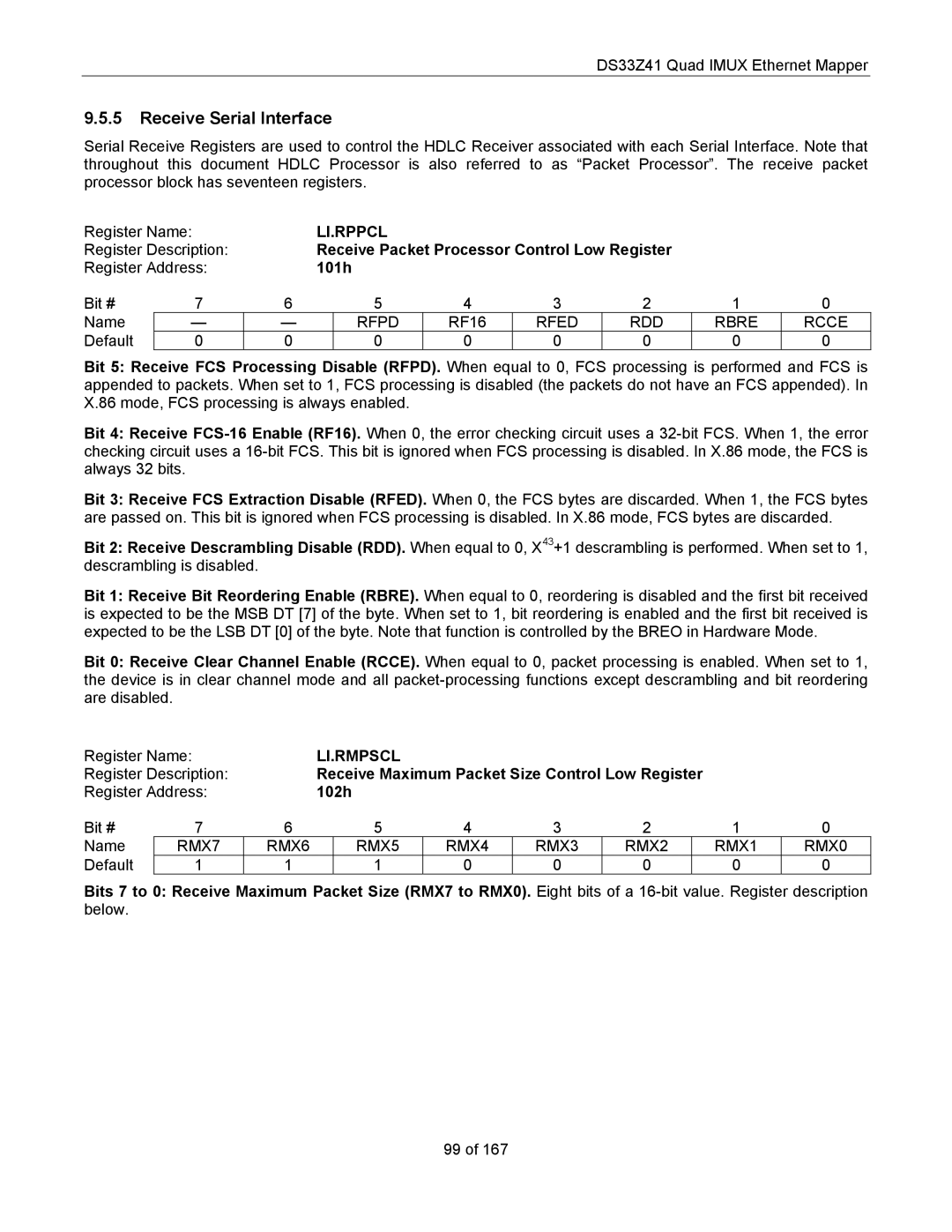

Serial Receive Registers are used to control the HDLC Receiver associated with each Serial Interface. Note that throughout this document HDLC Processor is also referred to as “Packet Processor”. The receive packet processor block has seventeen registers.

Register Name: |

| LI.RPPCL |

|

|

|

|

| ||

Register Description: |

| Receive Packet Processor Control Low Register |

|

| |||||

Register Address: |

| 101h |

|

|

|

|

| ||

Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

Name | — | — |

| RFPD | RF16 | RFED | RDD | RBRE | RCCE |

Default | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 |

Bit 5: Receive FCS Processing Disable (RFPD). When equal to 0, FCS processing is performed and FCS is appended to packets. When set to 1, FCS processing is disabled (the packets do not have an FCS appended). In X.86 mode, FCS processing is always enabled.

Bit 4: Receive

When 0, the error checking circuit uses a

Bit 3: Receive FCS Extraction Disable (RFED). When 0, the FCS bytes are discarded. When 1, the FCS bytes are passed on. This bit is ignored when FCS processing is disabled. In X.86 mode, FCS bytes are discarded.

Bit 2: Receive Descrambling Disable (RDD). When equal to 0, X43+1 descrambling is performed. When set to 1, descrambling is disabled.

Bit 1: Receive Bit Reordering Enable (RBRE). When equal to 0, reordering is disabled and the first bit received is expected to be the MSB DT [7] of the byte. When set to 1, bit reordering is enabled and the first bit received is expected to be the LSB DT [0] of the byte. Note that function is controlled by the BREO in Hardware Mode.

Bit 0: Receive Clear Channel Enable (RCCE). When equal to 0, packet processing is enabled. When set to 1, the device is in clear channel mode and all

Register Name: |

| LI.RMPSCL |

|

|

|

|

|

| ||

Register Description: |

| Receive Maximum Packet Size Control Low Register |

|

| ||||||

Register Address: |

| 102h |

|

|

|

|

|

| ||

Bit # | 7 | 6 | 5 | 4 | 3 | 2 |

| 1 | 0 | |

Name | RMX7 | RMX6 |

| RMX5 | RMX4 | RMX3 | RMX2 |

| RMX1 | RMX0 |

Default | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 0 | 0 |

Bits 7 to 0: Receive Maximum Packet Size (RMX7 to RMX0). Eight bits of a

below.

99 of 167