DS33Z41 Quad IMUX Ethernet Mapper

Register Name: |

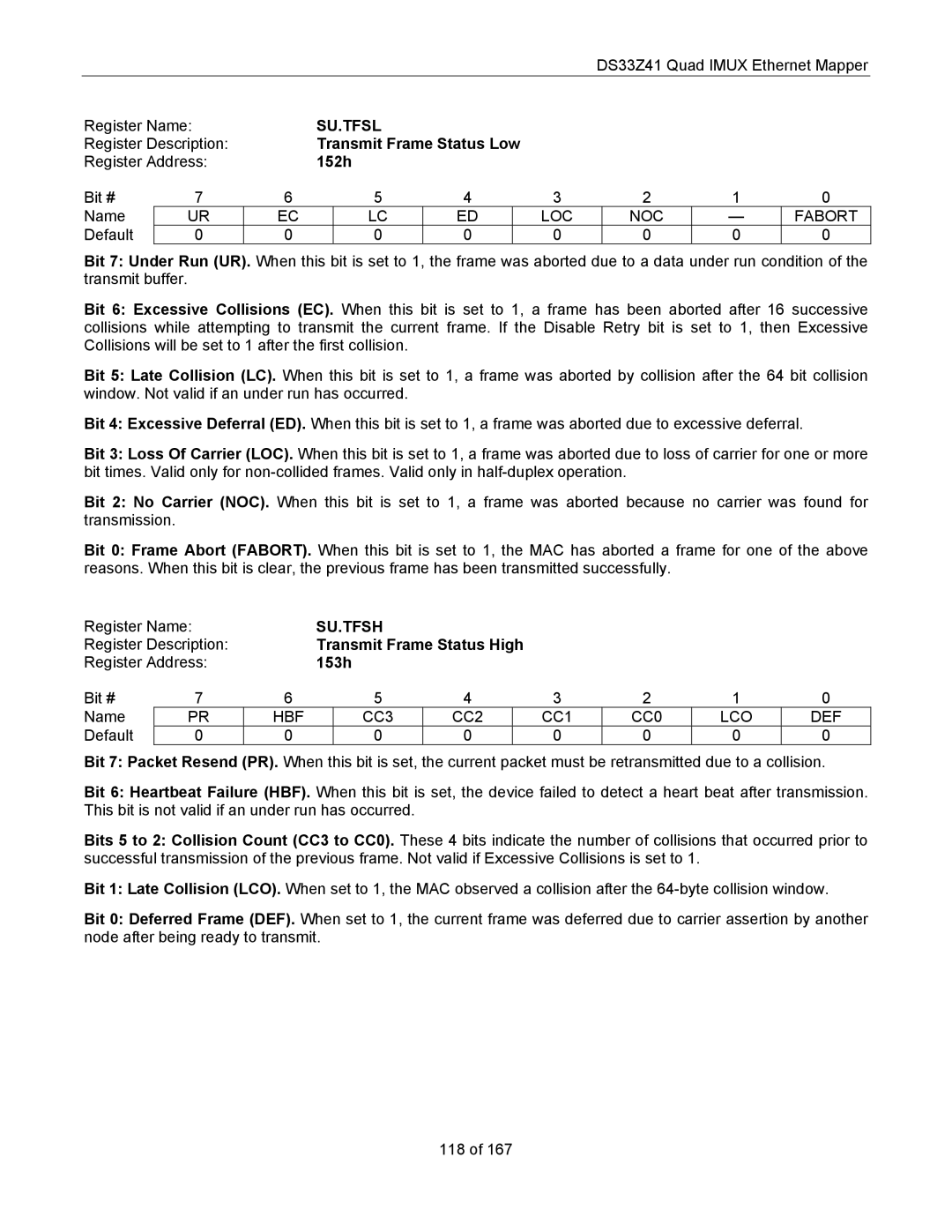

| SU.TFSL |

|

|

|

|

|

| ||

Register Description: |

| Transmit Frame Status Low |

|

|

|

| ||||

Register Address: |

| 152h |

|

|

|

|

|

| ||

Bit # | 7 | 6 | 5 | 4 |

| 3 | 2 | 1 | 0 | |

Name | UR | EC |

| LC | ED |

| LOC | NOC | — | FABORT |

Default | 0 | 0 |

| 0 | 0 |

| 0 | 0 | 0 | 0 |

Bit 7: Under Run (UR). When this bit is set to 1, the frame was aborted due to a data under run condition of the transmit buffer.

Bit 6: Excessive Collisions (EC). When this bit is set to 1, a frame has been aborted after 16 successive collisions while attempting to transmit the current frame. If the Disable Retry bit is set to 1, then Excessive Collisions will be set to 1 after the first collision.

Bit 5: Late Collision (LC). When this bit is set to 1, a frame was aborted by collision after the 64 bit collision window. Not valid if an under run has occurred.

Bit 4: Excessive Deferral (ED). When this bit is set to 1, a frame was aborted due to excessive deferral.

Bit 3: Loss Of Carrier (LOC). When this bit is set to 1, a frame was aborted due to loss of carrier for one or more bit times. Valid only for

Bit 2: No Carrier (NOC). When this bit is set to 1, a frame was aborted because no carrier was found for transmission.

Bit 0: Frame Abort (FABORT). When this bit is set to 1, the MAC has aborted a frame for one of the above reasons. When this bit is clear, the previous frame has been transmitted successfully.

Register Name: |

| SU.TFSH |

|

|

|

|

|

| ||

Register Description: |

| Transmit Frame Status High |

|

|

|

| ||||

Register Address: |

| 153h |

|

|

|

|

|

| ||

Bit # | 7 | 6 | 5 | 4 |

| 3 | 2 | 1 | 0 | |

Name | PR | HBF |

| CC3 | CC2 |

| CC1 | CC0 | LCO | DEF |

Default | 0 | 0 |

| 0 | 0 |

| 0 | 0 | 0 | 0 |

Bit 7: Packet Resend (PR). When this bit is set, the current packet must be retransmitted due to a collision.

Bit 6: Heartbeat Failure (HBF). When this bit is set, the device failed to detect a heart beat after transmission. This bit is not valid if an under run has occurred.

Bits 5 to 2: Collision Count (CC3 to CC0). These 4 bits indicate the number of collisions that occurred prior to successful transmission of the previous frame. Not valid if Excessive Collisions is set to 1.

Bit 1: Late Collision (LCO). When set to 1, the MAC observed a collision after the

Bit 0: Deferred Frame (DEF). When set to 1, the current frame was deferred due to carrier assertion by another node after being ready to transmit.

118 of 167