DS33Z41 Quad IMUX Ethernet Mapper

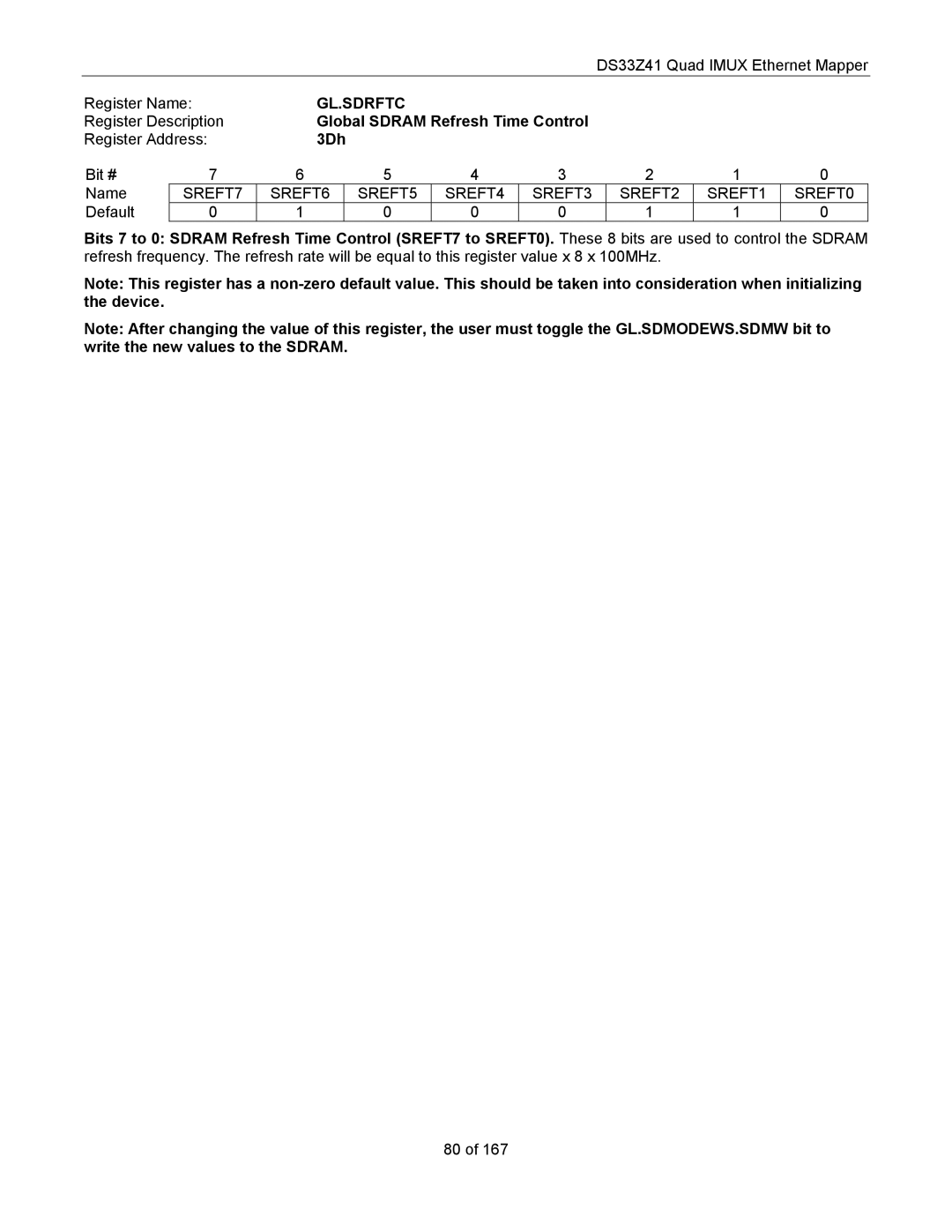

Register Name: | GL.SDRFTC |

Register Description | Global SDRAM Refresh Time Control |

Register Address: | 3Dh |

Bit #

Name

Default

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

SREFT7 | SREFT6 | SREFT5 | SREFT4 | SREFT3 | SREFT2 | SREFT1 | SREFT0 |

0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 |

Bits 7 to 0: SDRAM Refresh Time Control (SREFT7 to SREFT0). These 8 bits are used to control the SDRAM refresh frequency. The refresh rate will be equal to this register value x 8 x 100MHz.

Note: This register has a

Note: After changing the value of this register, the user must toggle the GL.SDMODEWS.SDMW bit to write the new values to the SDRAM.

80 of 167