DS33Z41 Quad IMUX Ethernet Mapper

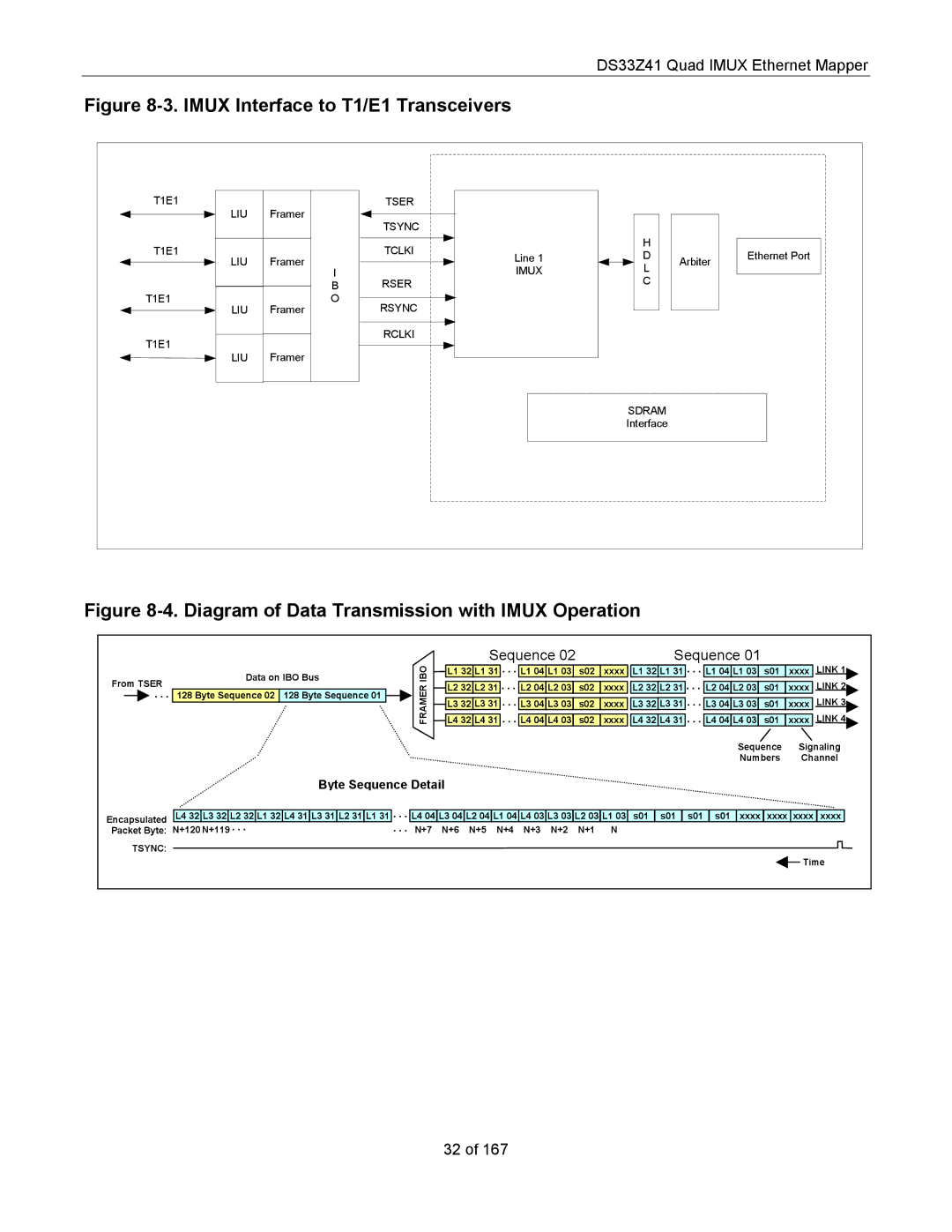

Figure 8-3. IMUX Interface to T1/E1 Transceivers

T1E1

T1E1

T1E1T1E1

T1E1

T1E1

LIU | Framer |

LIU | Framer |

| I |

| B |

| O |

LIU | Framer |

LIU | Framer |

TSER

TSYNC

TCLKI

RSER

RSYNC

RCLKI

Line 1

IMUX

H |

|

|

|

|

|

|

| ||

D |

| Arbiter |

| Ethernet Port |

L |

|

|

| |

|

|

|

| |

C |

|

|

|

|

|

|

|

|

|

SDRAM

Interface

Figure 8-4. Diagram of Data Transmission with IMUX Operation

|

|

| IBO |

|

| Sequence 02 |

|

|

| Sequence 01 |

|

|

| |||||||

From TSER | Data on IBO Bus | L1 32 L1 31 . . . | L1 | 04 | L1 03 |

| s02 | xxxx | L1 32 L1 31 . . . | L1 04 L1 03 | s01 | xxxx | LINK 1 | |||||||

128 Byte Sequence 02 | 128 Byte Sequence 01 | FRAMER | L2 32 L2 | 31 . . . | L2 | 04 | L2 03 |

| s02 | xxxx | L2 32 | L2 31 . . . | L2 04 L2 03 | s01 | xxxx | LINK 2 | ||||

. . . | L3 32 L3 | 31 . . . L3 | 04 L3 03 |

| s02 | xxxx | L3 32 | L3 31 . . . | L3 04 L3 03 | s01 | xxxx | LINK 3 | ||||||||

|

|

|

| |||||||||||||||||

|

|

| L4 32 L4 | 31 . . . | L4 | 04 | L4 03 |

| s02 | xxxx | L4 32 | L4 31 . . . | L4 04 L4 03 | s01 | xxxx | LINK 4 | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Sequence | Signaling | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Numbers | Channel | ||

|

| Byte Sequence Detail |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

Encapsulated | L4 32 L3 32 L2 32 L1 32 L4 31 L3 31 L2 31 L1 31 . . . | L4 04 L3 04 L2 04 L1 04 L4 | 03 | L3 03 | L2 03 L1 03 | s01 | s01 | s01 | s01 | xxxx | xxxx xxxx | xxxx | ||||||||

Packet Byte: N+120 N+119 . . . | . . . | N+7 | N+6 | N+5 | N+4 | N+3 | N+2 |

| N+1 | N |

|

|

|

|

|

|

|

| ||

TSYNC: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Time | |

32 of 167