DS33Z41 Quad IMUX Ethernet Mapper

9.3Arbiter Registers

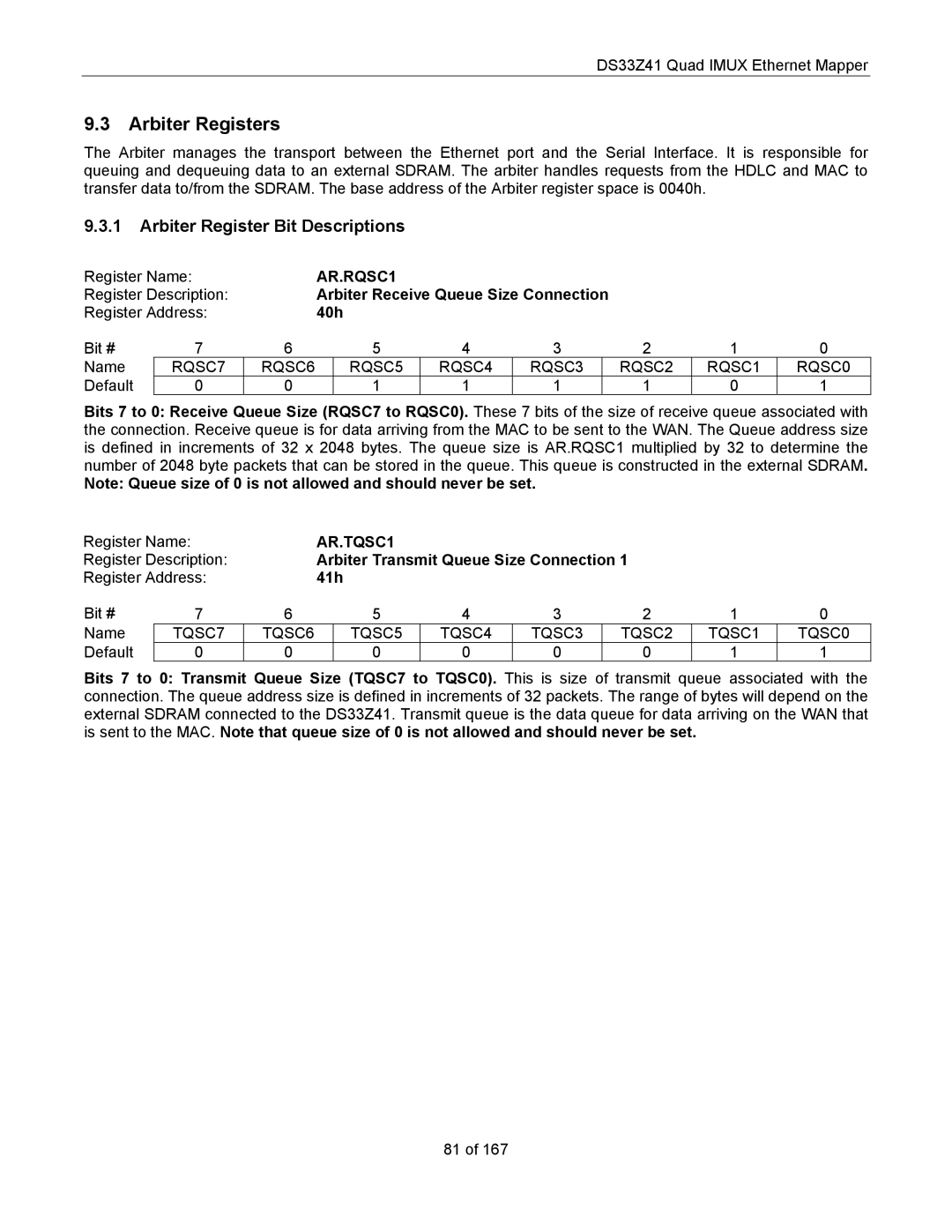

The Arbiter manages the transport between the Ethernet port and the Serial Interface. It is responsible for queuing and dequeuing data to an external SDRAM. The arbiter handles requests from the HDLC and MAC to transfer data to/from the SDRAM. The base address of the Arbiter register space is 0040h.

9.3.1Arbiter Register Bit Descriptions

Register Name: |

| AR.RQSC1 |

|

|

|

|

|

| ||

Register Description: |

| Arbiter Receive Queue Size Connection |

|

|

| |||||

Register Address: |

| 40h |

|

|

|

|

|

| ||

Bit # | 7 | 6 | 5 | 4 | 3 |

| 2 | 1 | 0 | |

Name | RQSC7 | RQSC6 |

| RQSC5 | RQSC4 | RQSC3 |

| RQSC2 | RQSC1 | RQSC0 |

Default | 0 | 0 |

| 1 | 1 | 1 |

| 1 | 0 | 1 |

Bits 7 to 0: Receive Queue Size (RQSC7 to RQSC0). These 7 bits of the size of receive queue associated with the connection. Receive queue is for data arriving from the MAC to be sent to the WAN. The Queue address size is defined in increments of 32 x 2048 bytes. The queue size is AR.RQSC1 multiplied by 32 to determine the number of 2048 byte packets that can be stored in the queue. This queue is constructed in the external SDRAM.

Note: Queue size of 0 is not allowed and should never be set.

Register Name: |

| AR.TQSC1 |

|

|

|

|

| ||

Register Description: |

| Arbiter Transmit Queue Size Connection 1 |

|

| |||||

Register Address: |

| 41h |

|

|

|

|

| ||

Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

Name | TQSC7 | TQSC6 |

| TQSC5 | TQSC4 | TQSC3 | TQSC2 | TQSC1 | TQSC0 |

Default | 0 | 0 |

| 0 | 0 | 0 | 0 | 1 | 1 |

Bits 7 to 0: Transmit Queue Size (TQSC7 to TQSC0). This is size of transmit queue associated with the connection. The queue address size is defined in increments of 32 packets. The range of bytes will depend on the external SDRAM connected to the DS33Z41. Transmit queue is the data queue for data arriving on the WAN that is sent to the MAC. Note that queue size of 0 is not allowed and should never be set.

81 of 167