DS33Z41 Quad IMUX Ethernet Mapper

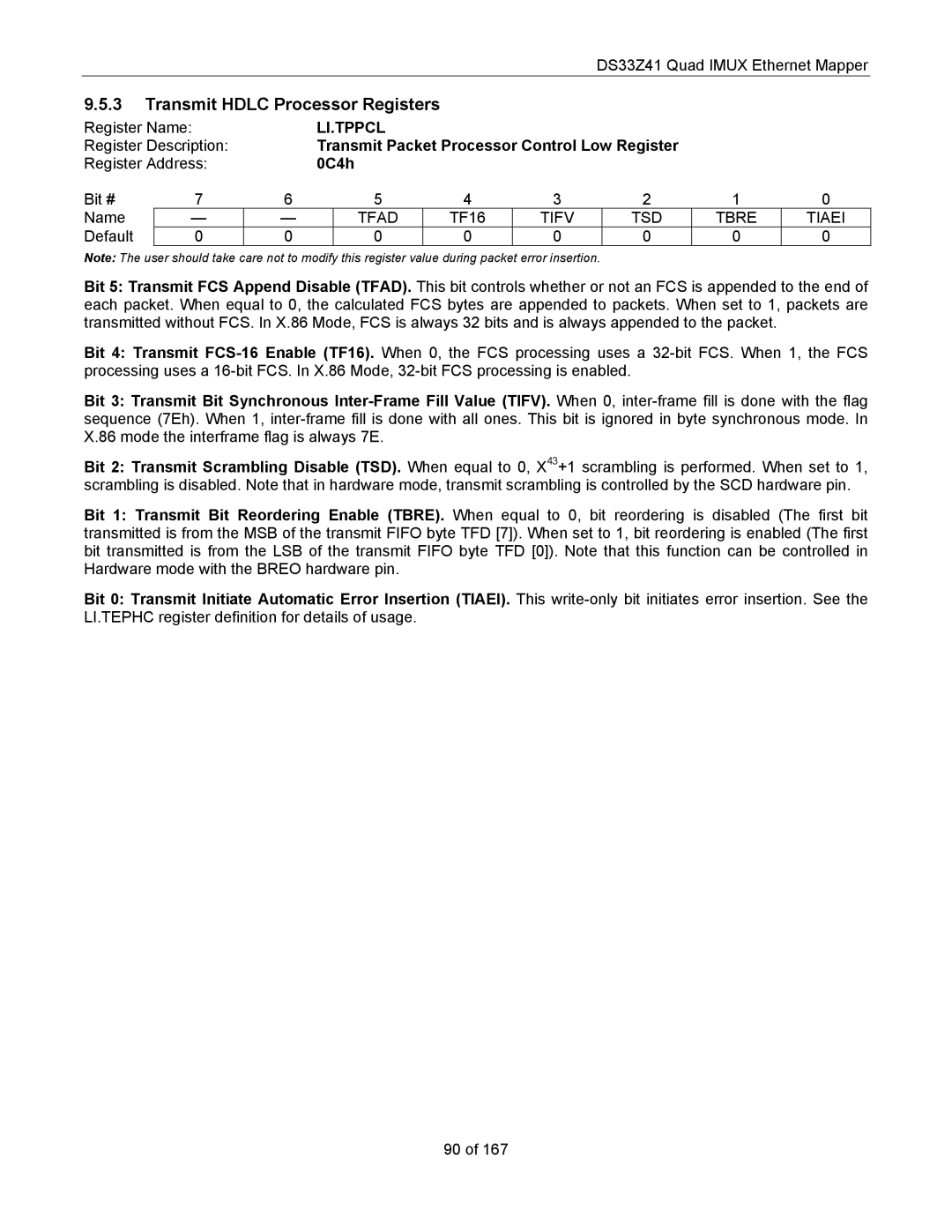

9.5.3Transmit HDLC Processor Registers

Register Name: |

| LI.TPPCL |

|

|

|

|

| ||

Register Description: |

| Transmit Packet Processor Control Low Register |

|

| |||||

Register Address: |

| 0C4h |

|

|

|

|

| ||

Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

Name | — | — |

| TFAD | TF16 | TIFV | TSD | TBRE | TIAEI |

Default | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 |

Note: The user should take care not to modify this register value during packet error insertion.

Bit 5: Transmit FCS Append Disable (TFAD). This bit controls whether or not an FCS is appended to the end of each packet. When equal to 0, the calculated FCS bytes are appended to packets. When set to 1, packets are transmitted without FCS. In X.86 Mode, FCS is always 32 bits and is always appended to the packet.

Bit 4: Transmit

Bit 3: Transmit Bit Synchronous

Bit 2: Transmit Scrambling Disable (TSD). When equal to 0, X43+1 scrambling is performed. When set to 1, scrambling is disabled. Note that in hardware mode, transmit scrambling is controlled by the SCD hardware pin.

Bit 1: Transmit Bit Reordering Enable (TBRE). When equal to 0, bit reordering is disabled (The first bit transmitted is from the MSB of the transmit FIFO byte TFD [7]). When set to 1, bit reordering is enabled (The first bit transmitted is from the LSB of the transmit FIFO byte TFD [0]). Note that this function can be controlled in Hardware mode with the BREO hardware pin.

Bit 0: Transmit Initiate Automatic Error Insertion (TIAEI). This

LI.TEPHC register definition for details of usage.

90 of 167