DS33Z41 Quad IMUX Ethernet Mapper

Register Name: | SU.MACFCR |

|

|

|

|

|

|

| ||

Register Description: | MAC Flow Control Register |

|

|

|

|

| ||||

Register Address: | 001Ch (indirect) |

|

|

|

|

| ||||

001Ch: |

|

|

|

|

|

|

|

|

|

|

Bit # | 31 | 30 | 29 | 28 |

| 27 | 26 | 25 | 24 |

|

Name | PT15 | PT14 | PT13 | PT12 |

| PT11 | PT10 | PT09 | PT08 | |

Default | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 |

|

001Dh: |

|

|

|

|

|

|

|

|

|

|

Bit # | 23 | 22 | 21 | 20 |

| 19 | 18 | 17 | 16 |

|

Name | PT07 | PT06 | PT05 | PT04 |

| PT03 | PT02 | PT01 | PT00 | |

Default | 0 | 1 | 0 | 1 |

| 0 | 0 | 0 | 0 |

|

001Eh: |

|

|

|

|

|

|

|

|

|

|

Bit # | 15 | 14 | 13 | 12 |

| 11 | 10 | 09 | 08 |

|

Name | Reserved | Reserved | Reserved | Reserved |

| Reserved | Reserved | Reserved | Reserved | |

Default | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 |

|

001Fh: |

|

|

|

|

|

|

|

|

|

|

Bit # | 07 | 06 | 05 | 04 |

| 03 | 02 | 01 | 00 |

|

Name | Reserved | Reserved | Reserved | Reserved |

| Reserved | Reserved | FCE | FCB |

|

Default | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

|

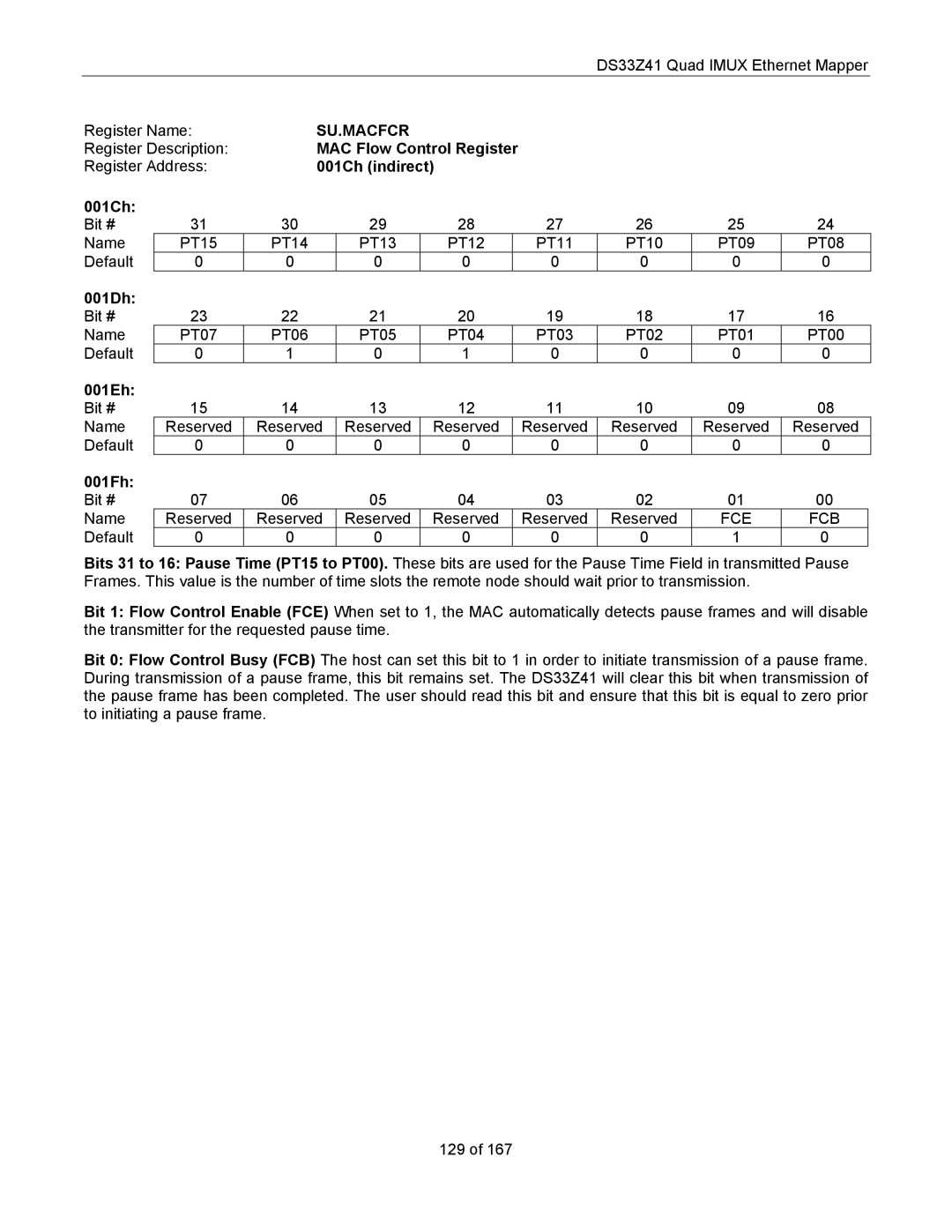

Bits 31 to 16: Pause Time (PT15 to PT00). These bits are used for the Pause Time Field in transmitted Pause Frames. This value is the number of time slots the remote node should wait prior to transmission.

Bit 1: Flow Control Enable (FCE) When set to 1, the MAC automatically detects pause frames and will disable the transmitter for the requested pause time.

Bit 0: Flow Control Busy (FCB) The host can set this bit to 1 in order to initiate transmission of a pause frame. During transmission of a pause frame, this bit remains set. The DS33Z41 will clear this bit when transmission of the pause frame has been completed. The user should read this bit and ensure that this bit is equal to zero prior to initiating a pause frame.

129 of 167