DS33Z41 Quad IMUX Ethernet Mapper

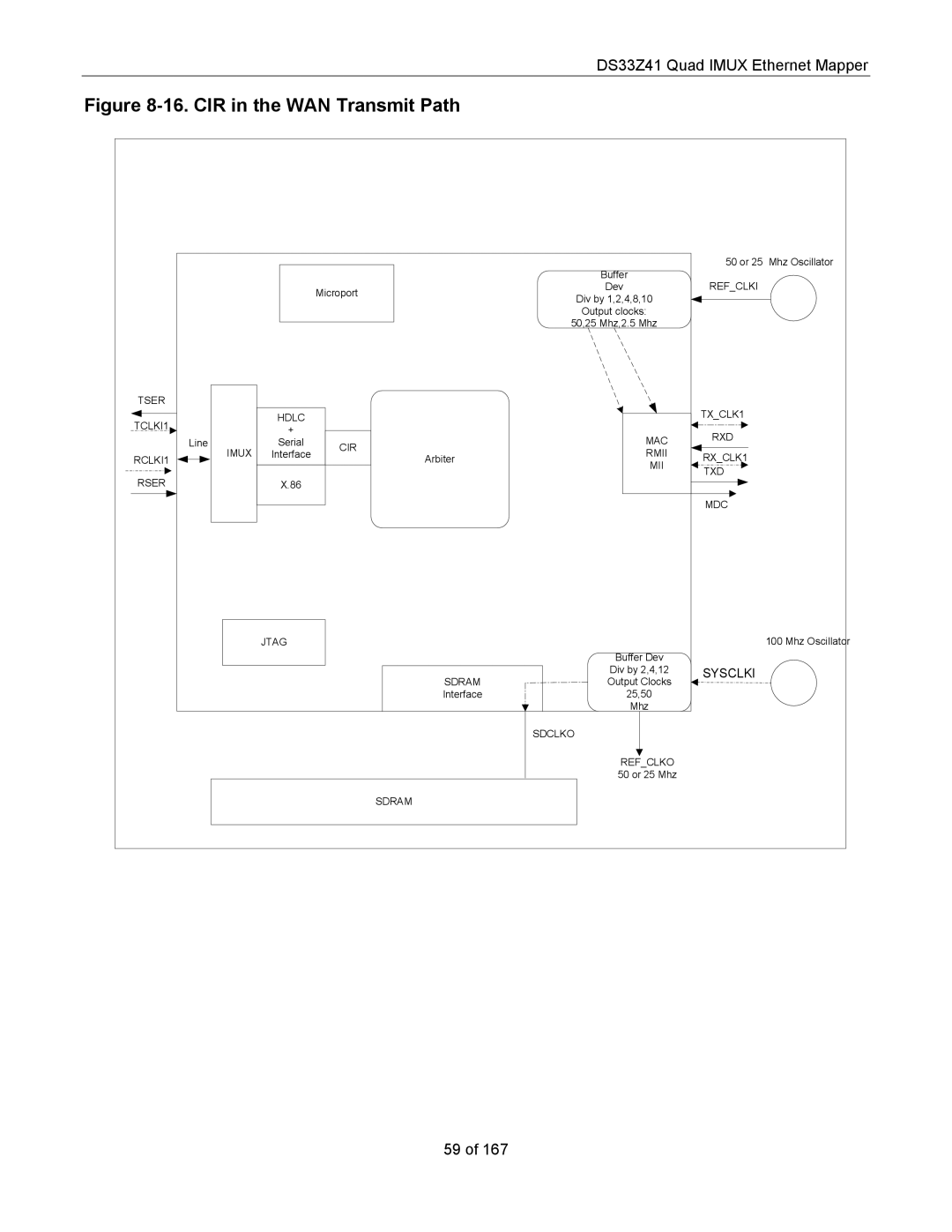

Figure 8-16. CIR in the WAN Transmit Path

|

|

|

| Buffer | 50 or 25 | Mhz Oscillator |

|

|

|

| REF_CLKI |

| |

|

|

| Microport | Dev |

| |

|

|

| Div by 1,2,4,8,10 |

|

| |

|

|

|

|

|

| |

|

|

|

| Output clocks: |

|

|

|

|

|

| 50,25 Mhz,2.5 Mhz |

|

|

TSER |

|

|

|

|

|

|

TCLKI1 |

| HDLC |

|

| TX_CLK1 |

|

| + |

|

| RXD |

| |

|

|

| MAC |

| ||

| Line 1 | Serial | CIR |

| ||

|

|

| ||||

| IMUX | Interface | RMII | RX_CLK1 |

| |

RCLKI1 | Arbiter |

| ||||

|

| MII |

| |||

|

|

|

| TXD |

| |

RSER |

| X.86 |

|

|

| |

|

|

|

|

| ||

|

|

|

|

| MDC |

|

|

| JTAG |

|

|

| 100 Mhz Oscillator |

|

|

|

| Buffer Dev |

|

|

|

|

| SDRAM | Div by 2,4,12 | SYSCLKI |

|

|

|

| Output Clocks |

|

| |

|

|

| Interface | 25,50 |

|

|

|

|

|

| Mhz |

|

|

|

|

|

| SDCLKO |

|

|

|

|

|

| REF_CLKO |

|

|

|

|

|

| 50 or 25 Mhz |

|

|

|

|

| SDRAM |

|

|

|

59 of 167