DS33Z41 Quad IMUX Ethernet Mapper

Register Name: |

| SU.RFRC |

|

|

|

|

| ||

Register Description: |

| Receive Frame Rejection Control |

|

|

| ||||

Register Address: |

| 15Eh |

|

|

|

|

| ||

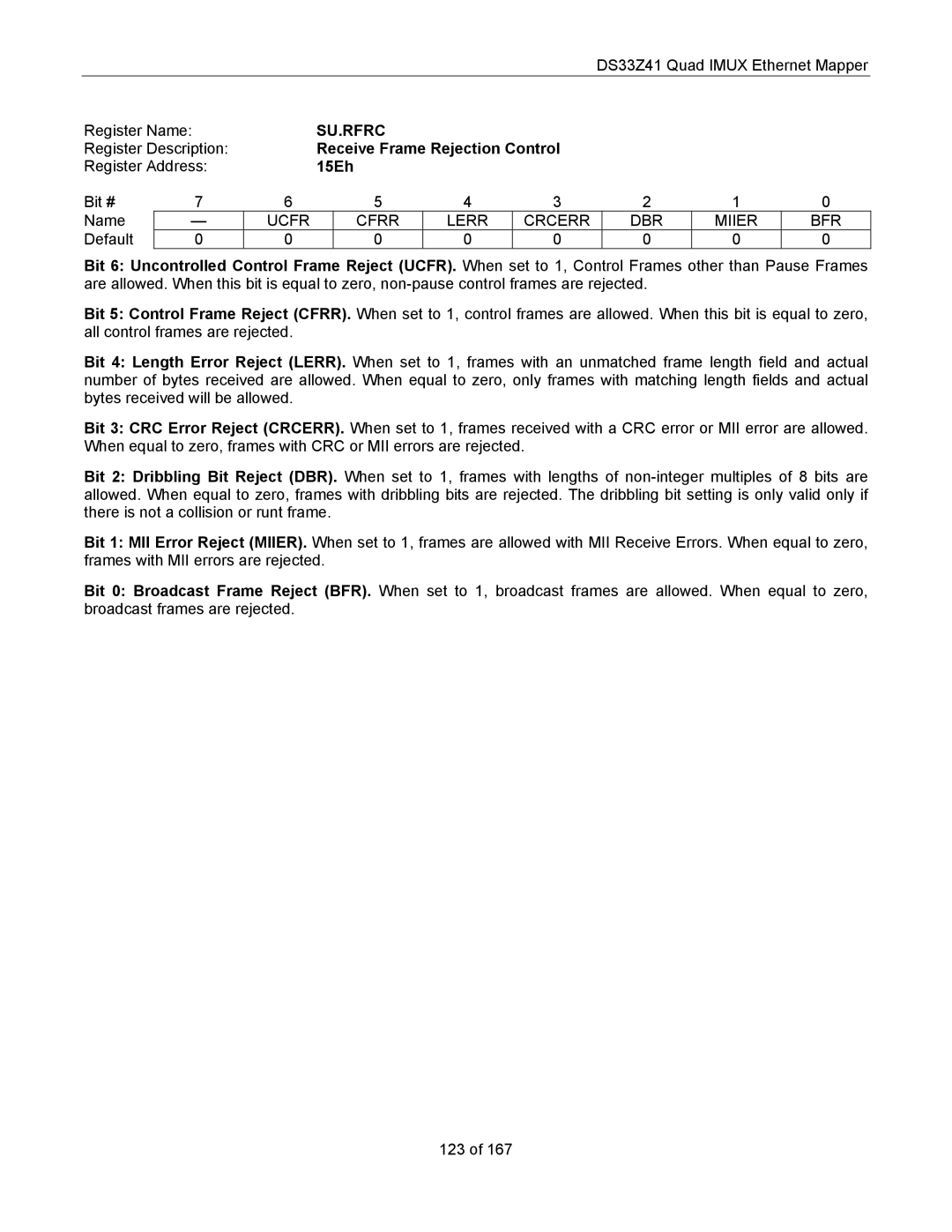

Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

Name | — | UCFR |

| CFRR | LERR | CRCERR | DBR | MIIER | BFR |

Default | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 |

Bit 6: Uncontrolled Control Frame Reject (UCFR). When set to 1, Control Frames other than Pause Frames are allowed. When this bit is equal to zero,

Bit 5: Control Frame Reject (CFRR). When set to 1, control frames are allowed. When this bit is equal to zero, all control frames are rejected.

Bit 4: Length Error Reject (LERR). When set to 1, frames with an unmatched frame length field and actual number of bytes received are allowed. When equal to zero, only frames with matching length fields and actual bytes received will be allowed.

Bit 3: CRC Error Reject (CRCERR). When set to 1, frames received with a CRC error or MII error are allowed. When equal to zero, frames with CRC or MII errors are rejected.

Bit 2: Dribbling Bit Reject (DBR). When set to 1, frames with lengths of

Bit 1: MII Error Reject (MIIER). When set to 1, frames are allowed with MII Receive Errors. When equal to zero, frames with MII errors are rejected.

Bit 0: Broadcast Frame Reject (BFR). When set to 1, broadcast frames are allowed. When equal to zero, broadcast frames are rejected.

123 of 167