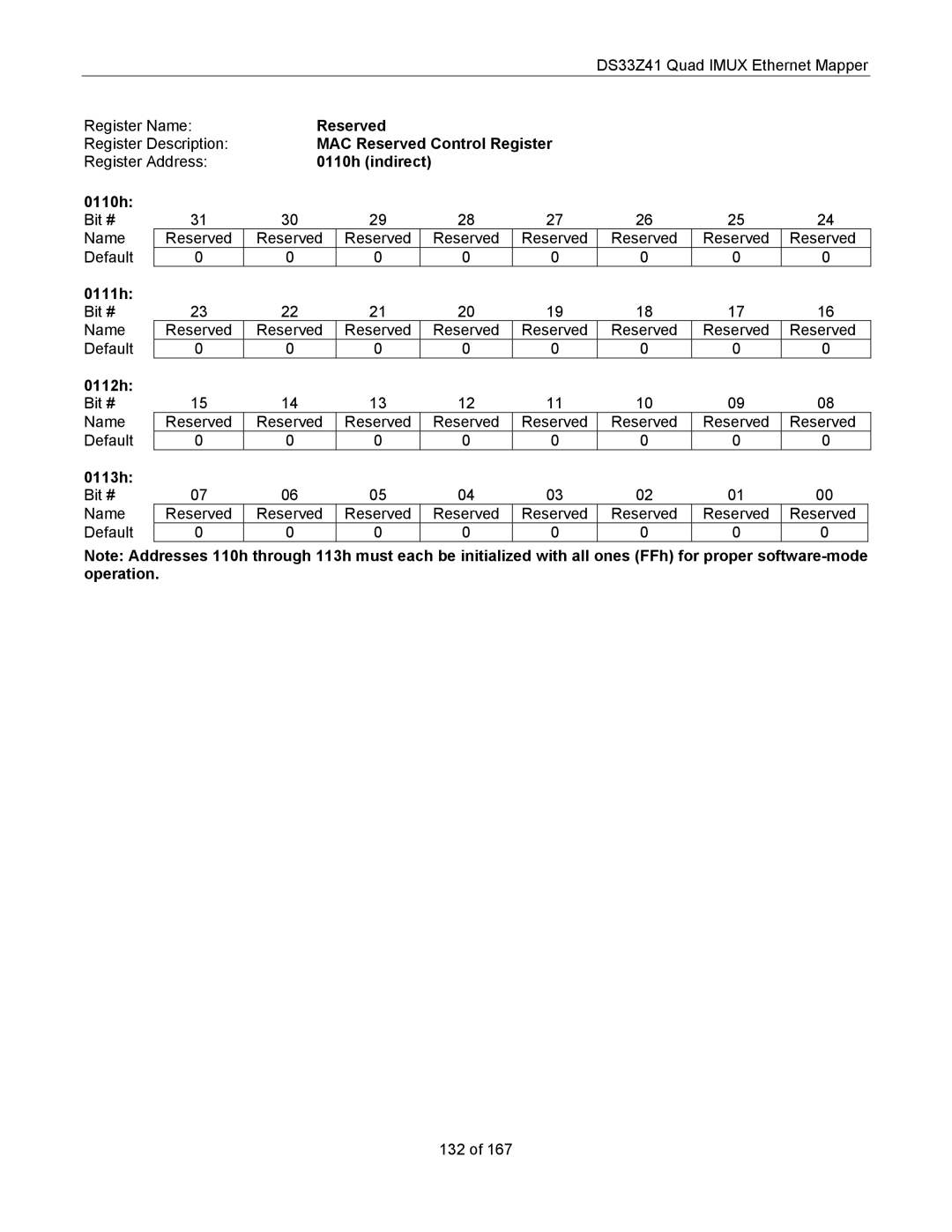

DS33Z41 Quad IMUX Ethernet Mapper

Register Name: | Reserved |

|

|

|

|

|

| |||

Register Description: | MAC Reserved Control Register |

|

|

|

| |||||

Register Address: | 0110h (indirect) |

|

|

|

|

|

| |||

0110h: |

|

|

|

|

|

|

|

|

|

|

Bit # | 31 | 30 | 29 |

| 28 | 27 | 26 | 25 | 24 |

|

Name | Reserved | Reserved | Reserved |

| Reserved | Reserved | Reserved | Reserved | Reserved | |

Default | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 |

|

0111h: |

|

|

|

|

|

|

|

|

|

|

Bit # | 23 | 22 | 21 |

| 20 | 19 | 18 | 17 | 16 |

|

Name | Reserved | Reserved | Reserved |

| Reserved | Reserved | Reserved | Reserved | Reserved | |

Default | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 |

|

0112h: |

|

|

|

|

|

|

|

|

|

|

Bit # | 15 | 14 | 13 |

| 12 | 11 | 10 | 09 | 08 |

|

Name | Reserved | Reserved | Reserved |

| Reserved | Reserved | Reserved | Reserved | Reserved | |

Default | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 |

|

0113h: |

|

|

|

|

|

|

|

|

|

|

Bit # | 07 | 06 | 05 |

| 04 | 03 | 02 | 01 | 00 |

|

Name | Reserved | Reserved | Reserved |

| Reserved | Reserved | Reserved | Reserved | Reserved |

|

Default | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 |

|

Note: Addresses 110h through 113h must each be initialized with all ones (FFh) for proper

132 of 167