|

|

|

| DS33Z41 Quad IMUX Ethernet Mapper |

|

|

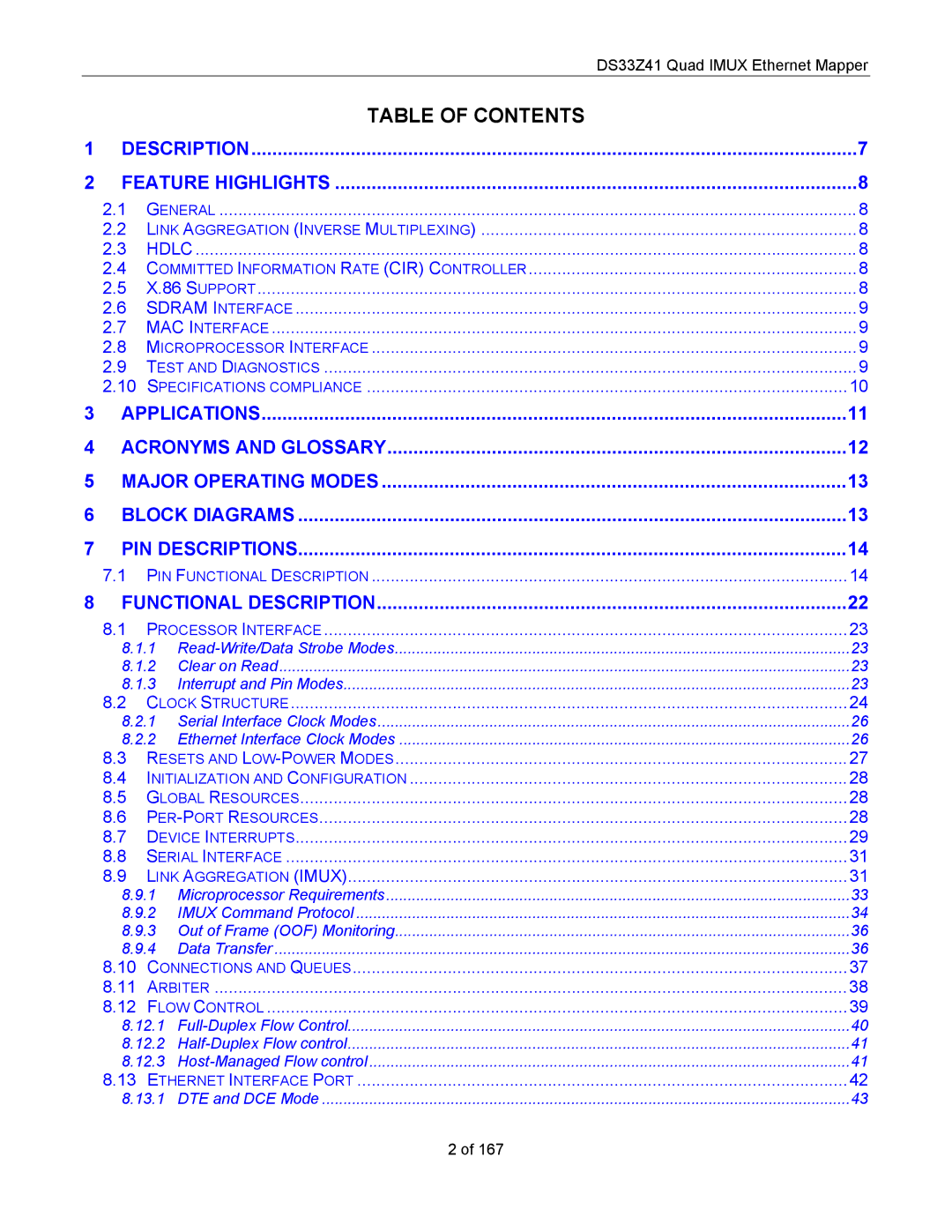

| TABLE OF CONTENTS |

|

1 | DESCRIPTION | 7 | ||

2 | FEATURE HIGHLIGHTS | 8 | ||

| 2.1 | GENERAL | 8 | |

| 2.2 | LINK AGGREGATION (INVERSE MULTIPLEXING) | 8 | |

| 2.3 | HDLC | 8 | |

| 2.4 | COMMITTED INFORMATION RATE (CIR) CONTROLLER | 8 | |

| 2.5 | X.86 SUPPORT | 8 | |

| 2.6 | SDRAM INTERFACE | 9 | |

| 2.7 | MAC INTERFACE | 9 | |

| 2.8 | MICROPROCESSOR INTERFACE | 9 | |

| 2.9 | TEST AND DIAGNOSTICS | 9 | |

| 2.10 | SPECIFICATIONS COMPLIANCE | 10 | |

3 | APPLICATIONS | 11 | ||

4 | ACRONYMS AND GLOSSARY | 12 | ||

5 | MAJOR OPERATING MODES | 13 | ||

6 | BLOCK DIAGRAMS | 13 | ||

7 | PIN DESCRIPTIONS | 14 | ||

| 7.1 | PIN FUNCTIONAL DESCRIPTION | 14 | |

8 | FUNCTIONAL DESCRIPTION | 22 | ||

| 8.1 | PROCESSOR INTERFACE | 23 | |

| 8.1.1 | 23 | ||

| 8.1.2 | Clear on Read | 23 | |

| 8.1.3 Interrupt and Pin Modes | 23 | ||

| 8.2 | CLOCK STRUCTURE | 24 | |

| 8.2.1 Serial Interface Clock Modes | 26 | ||

| 8.2.2 Ethernet Interface Clock Modes | 26 | ||

| 8.3 | RESETS AND | 27 | |

| 8.4 | INITIALIZATION AND CONFIGURATION | 28 | |

| 8.5 | GLOBAL RESOURCES | 28 | |

| 8.6 | 28 | ||

| 8.7 | DEVICE INTERRUPTS | 29 | |

| 8.8 | SERIAL INTERFACE | 31 | |

| 8.9 | LINK AGGREGATION (IMUX) | 31 | |

| 8.9.1 | Microprocessor Requirements | 33 | |

| 8.9.2 | IMUX Command Protocol | 34 | |

| 8.9.3 Out of Frame (OOF) Monitoring | 36 | ||

| 8.9.4 | Data Transfer | 36 | |

| 8.10 CONNECTIONS AND QUEUES | 37 | ||

| 8.11 | ARBITER | 38 | |

| 8.12 | FLOW CONTROL | 39 | |

| 8.12.1 | 40 | ||

| 8.12.2 | 41 | ||

| 8.12.3 | 41 | ||

| 8.13 | ETHERNET INTERFACE PORT | 42 | |

| 8.13.1 DTE and DCE Mode | 43 | ||

|

|

| 2 of 167 |

|

Page 2

Image 2