DS33Z41 Quad IMUX Ethernet Mapper

Register Name: |

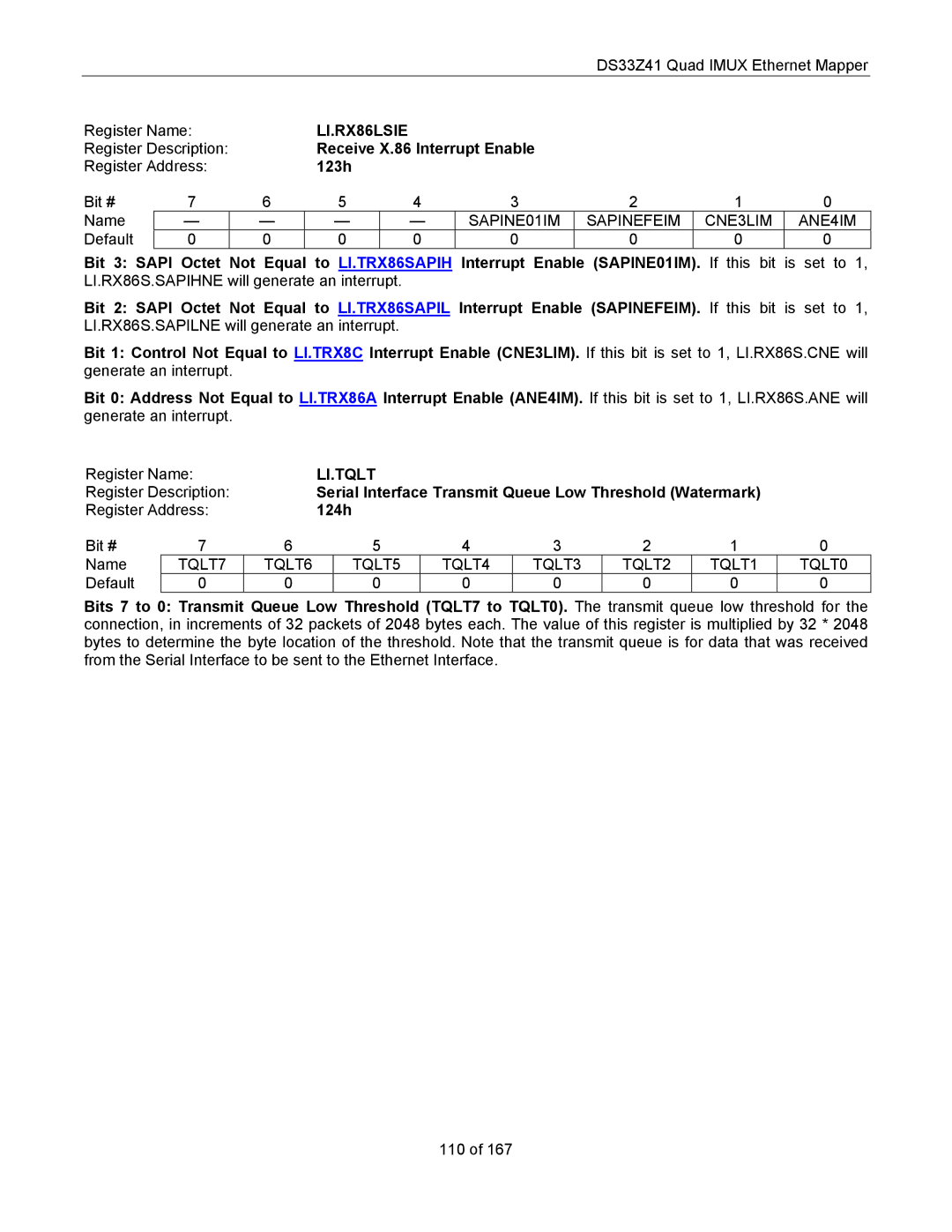

| LI.RX86LSIE |

|

|

|

|

| ||

Register Description: |

| Receive X.86 Interrupt Enable |

|

|

| ||||

Register Address: |

| 123h |

|

|

|

|

| ||

Bit # | 7 | 6 | 5 |

| 4 | 3 | 2 | 1 | 0 |

Name | — | — | — |

| — | SAPINE01IM | SAPINEFEIM | CNE3LIM | ANE4IM |

Default | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 |

Bit 3: SAPI Octet Not Equal to LI.TRX86SAPIH Interrupt Enable (SAPINE01IM). If this bit is set to 1, LI.RX86S.SAPIHNE will generate an interrupt.

Bit 2: SAPI Octet Not Equal to LI.TRX86SAPIL Interrupt Enable (SAPINEFEIM). If this bit is set to 1, LI.RX86S.SAPILNE will generate an interrupt.

Bit 1: Control Not Equal to LI.TRX8C Interrupt Enable (CNE3LIM). If this bit is set to 1, LI.RX86S.CNE will generate an interrupt.

Bit 0: Address Not Equal to LI.TRX86A Interrupt Enable (ANE4IM). If this bit is set to 1, LI.RX86S.ANE will generate an interrupt.

Register Name: |

| LI.TQLT |

|

|

|

|

| ||

Register Description: |

| Serial Interface Transmit Queue Low Threshold (Watermark) |

| ||||||

Register Address: |

| 124h |

|

|

|

|

| ||

Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

Name | TQLT7 | TQLT6 |

| TQLT5 | TQLT4 | TQLT3 | TQLT2 | TQLT1 | TQLT0 |

Default | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 |

Bits 7 to 0: Transmit Queue Low Threshold (TQLT7 to TQLT0). The transmit queue low threshold for the connection, in increments of 32 packets of 2048 bytes each. The value of this register is multiplied by 32 * 2048 bytes to determine the byte location of the threshold. Note that the transmit queue is for data that was received from the Serial Interface to be sent to the Ethernet Interface.

110 of 167