|

|

|

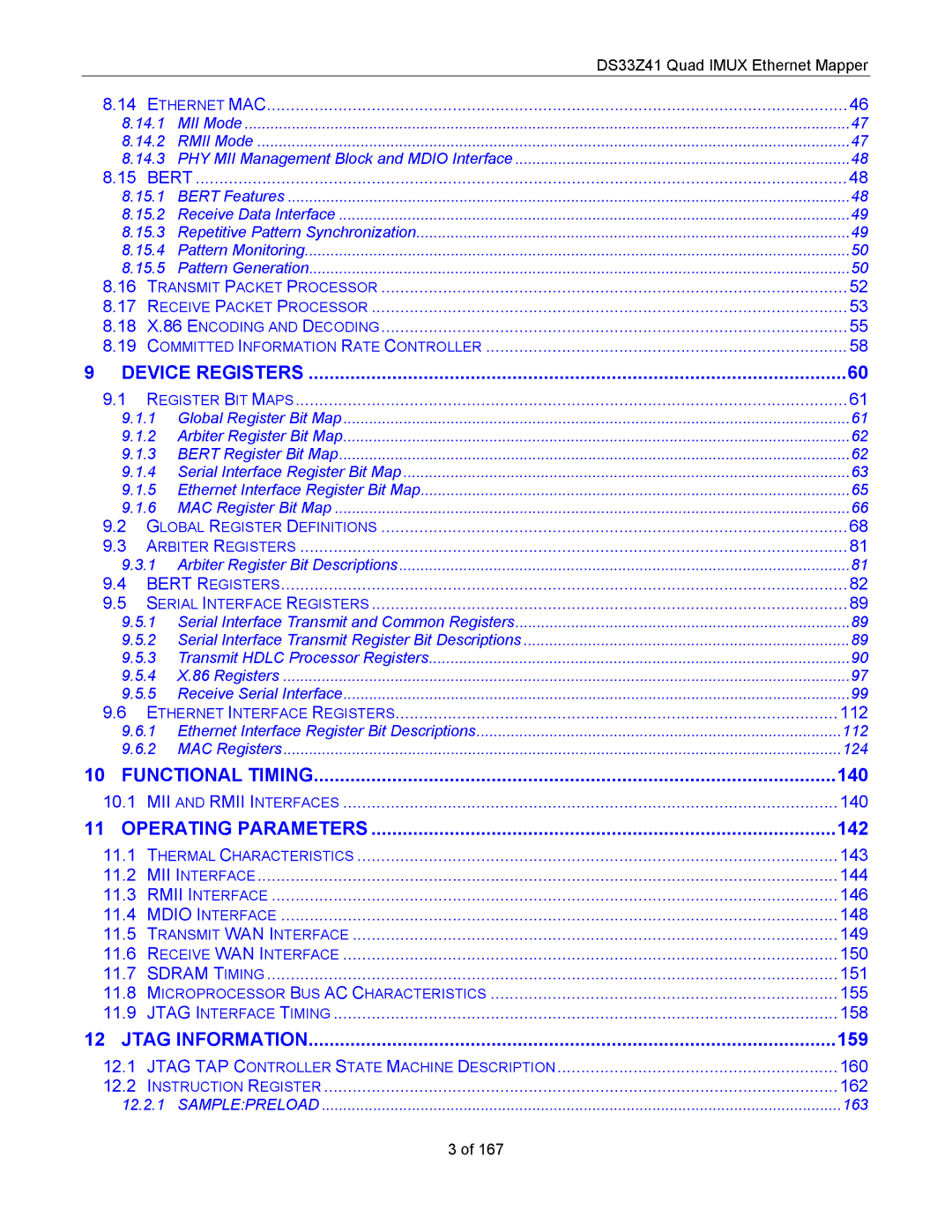

| DS33Z41 Quad IMUX Ethernet Mapper |

8.14 | ETHERNET MAC | 46 | ||

| 8.14.1 | MII Mode | 47 | |

| 8.14.2 | RMII Mode | 47 | |

| 8.14.3 | PHY MII Management Block and MDIO Interface | 48 | |

8.15 | BERT | 48 | ||

| 8.15.1 | BERT Features | 48 | |

| 8.15.2 | Receive Data Interface | 49 | |

| 8.15.3 | Repetitive Pattern Synchronization | 49 | |

| 8.15.4 | Pattern Monitoring | 50 | |

| 8.15.5 | Pattern Generation | 50 | |

8.16 | TRANSMIT PACKET PROCESSOR | 52 | ||

8.17 | RECEIVE PACKET PROCESSOR | 53 | ||

8.18 | X.86 ENCODING AND DECODING | 55 | ||

8.19 | COMMITTED INFORMATION RATE CONTROLLER | 58 | ||

9 | DEVICE REGISTERS | 60 | ||

9.1 | REGISTER BIT MAPS | 61 | ||

| 9.1.1 | Global Register Bit Map | 61 | |

| 9.1.2 | Arbiter Register Bit Map | 62 | |

| 9.1.3 | BERT Register Bit Map | 62 | |

| 9.1.4 | Serial Interface Register Bit Map | 63 | |

| 9.1.5 | Ethernet Interface Register Bit Map | 65 | |

| 9.1.6 | MAC Register Bit Map | 66 | |

9.2 | GLOBAL REGISTER DEFINITIONS | 68 | ||

9.3 | ARBITER REGISTERS | 81 | ||

| 9.3.1 | Arbiter Register Bit Descriptions | 81 | |

9.4 | BERT REGISTERS | 82 | ||

9.5 | SERIAL INTERFACE REGISTERS | 89 | ||

| 9.5.1 | Serial Interface Transmit and Common Registers | 89 | |

| 9.5.2 | Serial Interface Transmit Register Bit Descriptions | 89 | |

| 9.5.3 | Transmit HDLC Processor Registers | 90 | |

| 9.5.4 | X.86 Registers | 97 | |

| 9.5.5 | Receive Serial Interface | 99 | |

9.6 | ETHERNET INTERFACE REGISTERS | 112 | ||

| 9.6.1 | Ethernet Interface Register Bit Descriptions | 112 | |

| 9.6.2 | MAC Registers | 124 | |

10 | FUNCTIONAL TIMING | 140 | ||

10.1 | MII AND RMII INTERFACES | 140 | ||

11 | OPERATING PARAMETERS | 142 | ||

11.1 | THERMAL CHARACTERISTICS | 143 | ||

11.2 | MII INTERFACE | 144 | ||

11.3 | RMII INTERFACE | 146 | ||

11.4 | MDIO INTERFACE | 148 | ||

11.5 | TRANSMIT WAN INTERFACE | 149 | ||

11.6 | RECEIVE WAN INTERFACE | 150 | ||

11.7 | SDRAM TIMING | 151 | ||

11.8 | MICROPROCESSOR BUS AC CHARACTERISTICS | 155 | ||

11.9 | JTAG INTERFACE TIMING | 158 | ||

12 | JTAG INFORMATION | 159 | ||

12.1 | JTAG TAP CONTROLLER STATE MACHINE DESCRIPTION | 160 | ||

12.2 | INSTRUCTION REGISTER | 162 | ||

| 12.2.1 | SAMPLE:PRELOAD | 163 | |

|

|

| 3 of 167 |

|

Page 3

Image 3