DS33Z41 Quad IMUX Ethernet Mapper

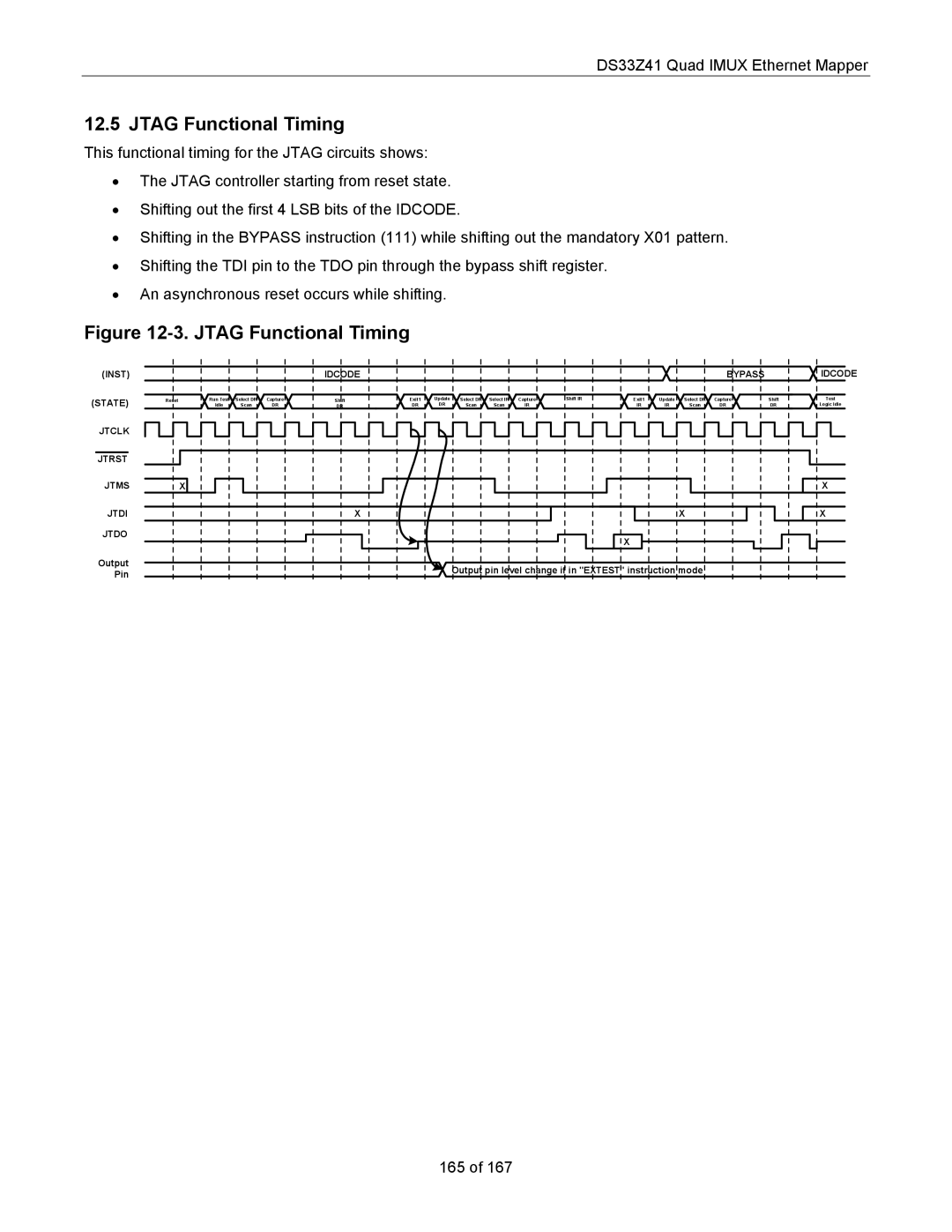

12.5 JTAG Functional Timing

This functional timing for the JTAG circuits shows:

•The JTAG controller starting from reset state.

•Shifting out the first 4 LSB bits of the IDCODE.

•Shifting in the BYPASS instruction (111) while shifting out the mandatory X01 pattern.

•Shifting the TDI pin to the TDO pin through the bypass shift register.

•An asynchronous reset occurs while shifting.

Figure 12-3. JTAG Functional Timing

(INST) |

|

|

|

| IDCODE |

|

|

|

|

|

|

|

|

| BYPASS |

|

| ||

|

|

|

|

|

|

| Update |

|

|

| Shift IR |

|

|

|

|

|

|

|

|

(STATE) | Reset | Run Test | Select DR | Capture | Shift | Exit1 | Select DR | Select IR | Capture | Exit1 | Update | Select DR | Capture |

| Shift |

| |||

| Idle | Scan | DR | DR | DR | DR | Scan | Scan | IR |

| IR | IR | Scan | DR |

|

| DR |

| |

JTCLK

JTRST

JTMS X

JTDI | X | X |

JTDO

X

Output | Output pin level change if in "EXTEST" instruction mode | |

Pin | ||

|

IDCODE

Test

Logic Idle

X

X

165 of 167