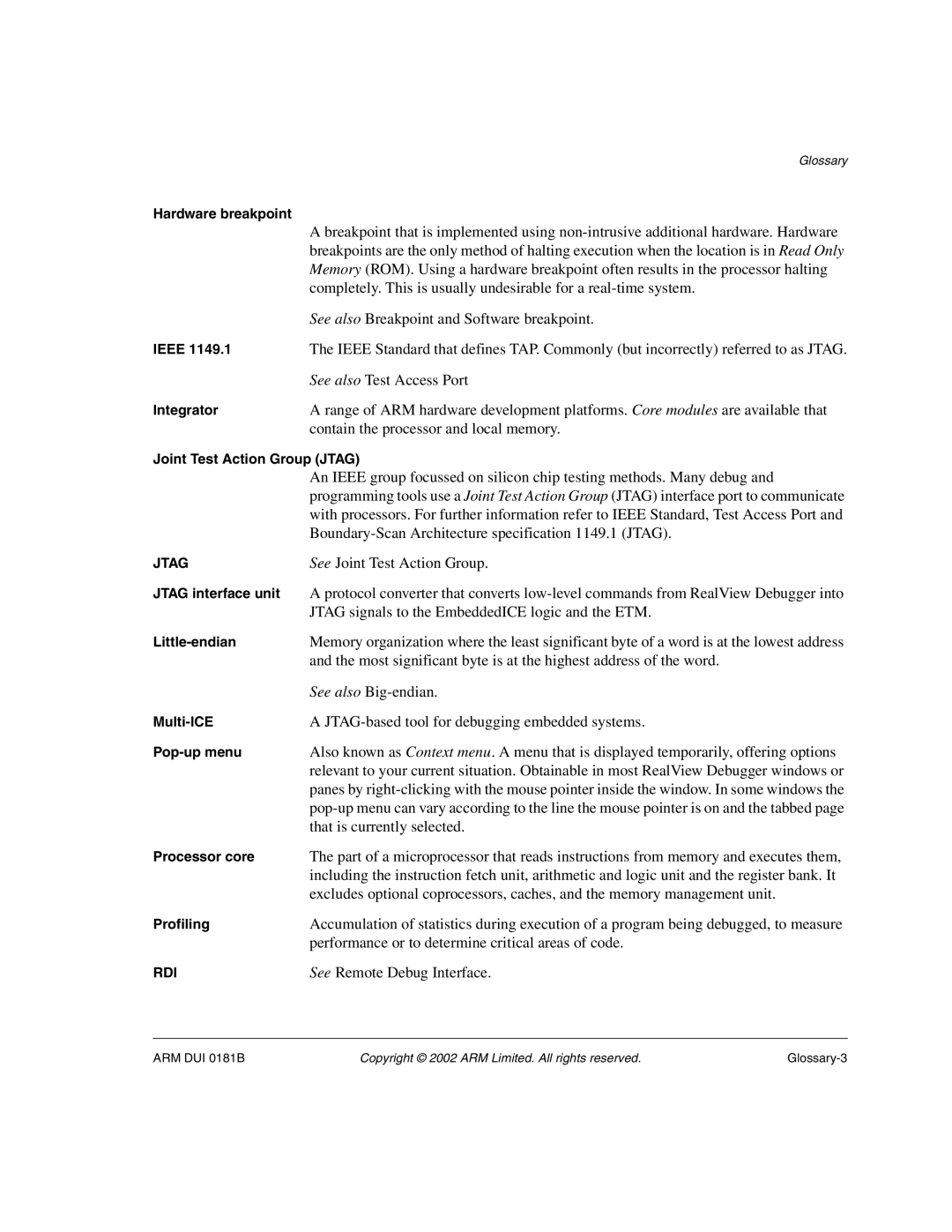

Glossary

Hardware breakpoint

| A breakpoint that is implemented using |

| breakpoints are the only method of halting execution when the location is in Read Only |

| Memory (ROM). Using a hardware breakpoint often results in the processor halting |

| completely. This is usually undesirable for a |

| See also Breakpoint and Software breakpoint. |

IEEE 1149.1 | The IEEE Standard that defines TAP. Commonly (but incorrectly) referred to as JTAG. |

| See also Test Access Port |

Integrator | A range of ARM hardware development platforms. Core modules are available that |

| contain the processor and local memory. |

Joint Test Action Group (JTAG)

An IEEE group focussed on silicon chip testing methods. Many debug and programming tools use a Joint Test Action Group (JTAG) interface port to communicate with processors. For further information refer to IEEE Standard, Test Access Port and

JTAG | See Joint Test Action Group. |

JTAG interface unit | A protocol converter that converts |

| JTAG signals to the EmbeddedICE logic and the ETM. |

Memory organization where the least significant byte of a word is at the lowest address | |

| and the most significant byte is at the highest address of the word. |

| See also |

A | |

Also known as Context menu. A menu that is displayed temporarily, offering options | |

| relevant to your current situation. Obtainable in most RealView Debugger windows or |

| panes by |

| |

| that is currently selected. |

Processor core | The part of a microprocessor that reads instructions from memory and executes them, |

| including the instruction fetch unit, arithmetic and logic unit and the register bank. It |

| excludes optional coprocessors, caches, and the memory management unit. |

Profiling | Accumulation of statistics during execution of a program being debugged, to measure |

| performance or to determine critical areas of code. |

RDI | See Remote Debug Interface. |

ARM DUI 0181B | Copyright © 2002 ARM Limited. All rights reserved. |