Functional Description

R

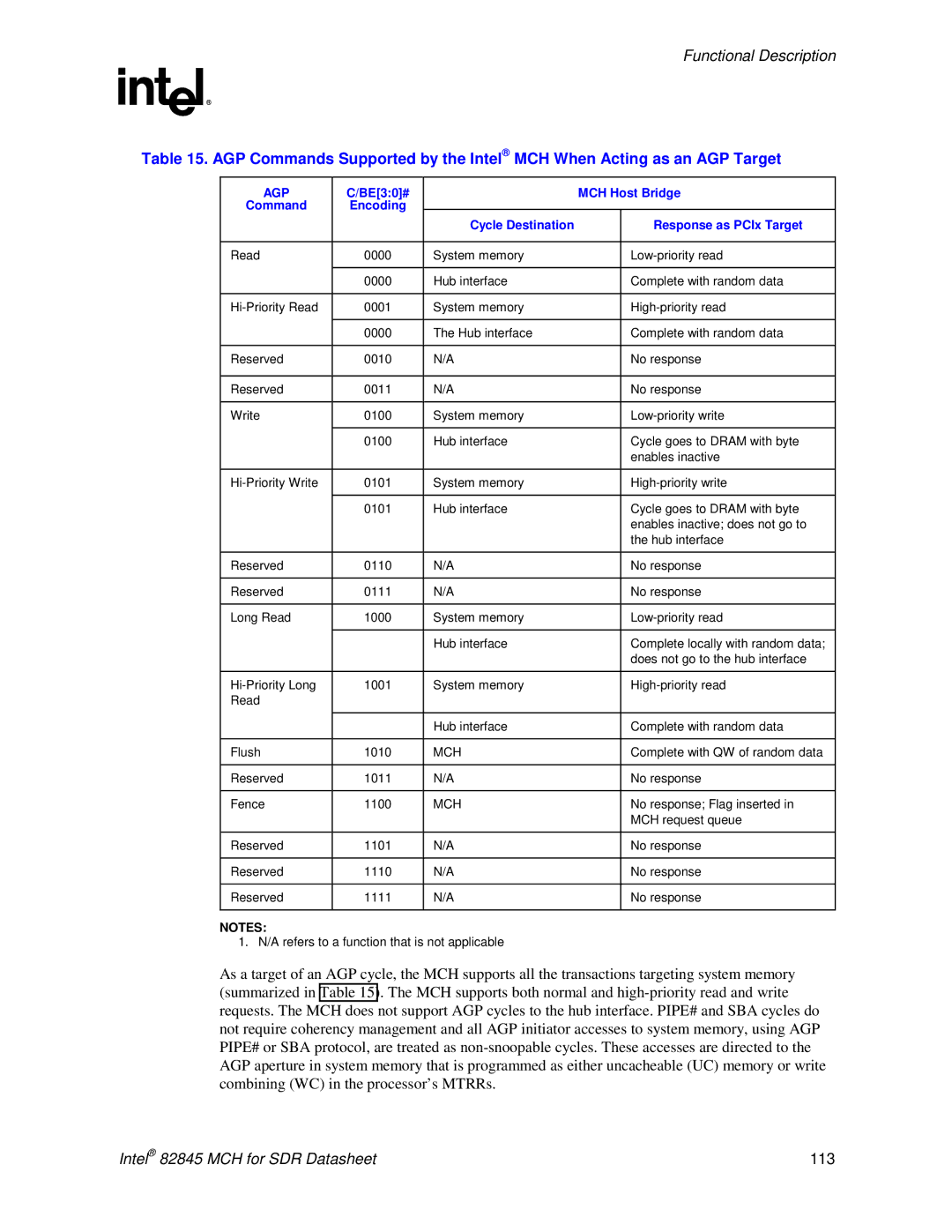

Table 15. AGP Commands Supported by the Intel® MCH When Acting as an AGP Target

AGP | C/BE[3:0]# |

| MCH Host Bridge | |

Command | Encoding |

|

|

|

|

| Cycle Destination |

| Response as PCIx Target |

|

|

|

|

|

Read | 0000 | System memory |

| |

|

|

|

|

|

| 0000 | Hub interface |

| Complete with random data |

|

|

|

|

|

0001 | System memory |

| ||

|

|

|

|

|

| 0000 | The Hub interface |

| Complete with random data |

|

|

|

|

|

Reserved | 0010 | N/A |

| No response |

|

|

|

|

|

Reserved | 0011 | N/A |

| No response |

|

|

|

|

|

Write | 0100 | System memory |

| |

|

|

|

|

|

| 0100 | Hub interface |

| Cycle goes to DRAM with byte |

|

|

|

| enables inactive |

|

|

|

|

|

0101 | System memory |

| ||

|

|

|

|

|

| 0101 | Hub interface |

| Cycle goes to DRAM with byte |

|

|

|

| enables inactive; does not go to |

|

|

|

| the hub interface |

|

|

|

|

|

Reserved | 0110 | N/A |

| No response |

|

|

|

|

|

Reserved | 0111 | N/A |

| No response |

|

|

|

|

|

Long Read | 1000 | System memory |

| |

|

|

|

|

|

|

| Hub interface |

| Complete locally with random data; |

|

|

|

| does not go to the hub interface |

|

|

|

|

|

1001 | System memory |

| ||

Read |

|

|

|

|

|

|

|

|

|

|

| Hub interface |

| Complete with random data |

|

|

|

|

|

Flush | 1010 | MCH |

| Complete with QW of random data |

|

|

|

|

|

Reserved | 1011 | N/A |

| No response |

|

|

|

|

|

Fence | 1100 | MCH |

| No response; Flag inserted in |

|

|

|

| MCH request queue |

|

|

|

|

|

Reserved | 1101 | N/A |

| No response |

|

|

|

|

|

Reserved | 1110 | N/A |

| No response |

|

|

|

|

|

Reserved | 1111 | N/A |

| No response |

|

|

|

|

|

NOTES:

1. N/A refers to a function that is not applicable

As a target of an AGP cycle, the MCH supports all the transactions targeting system memory (summarized in Table 15). The MCH supports both normal and

Intel® 82845 MCH for SDR Datasheet | 113 |