Register Description

R

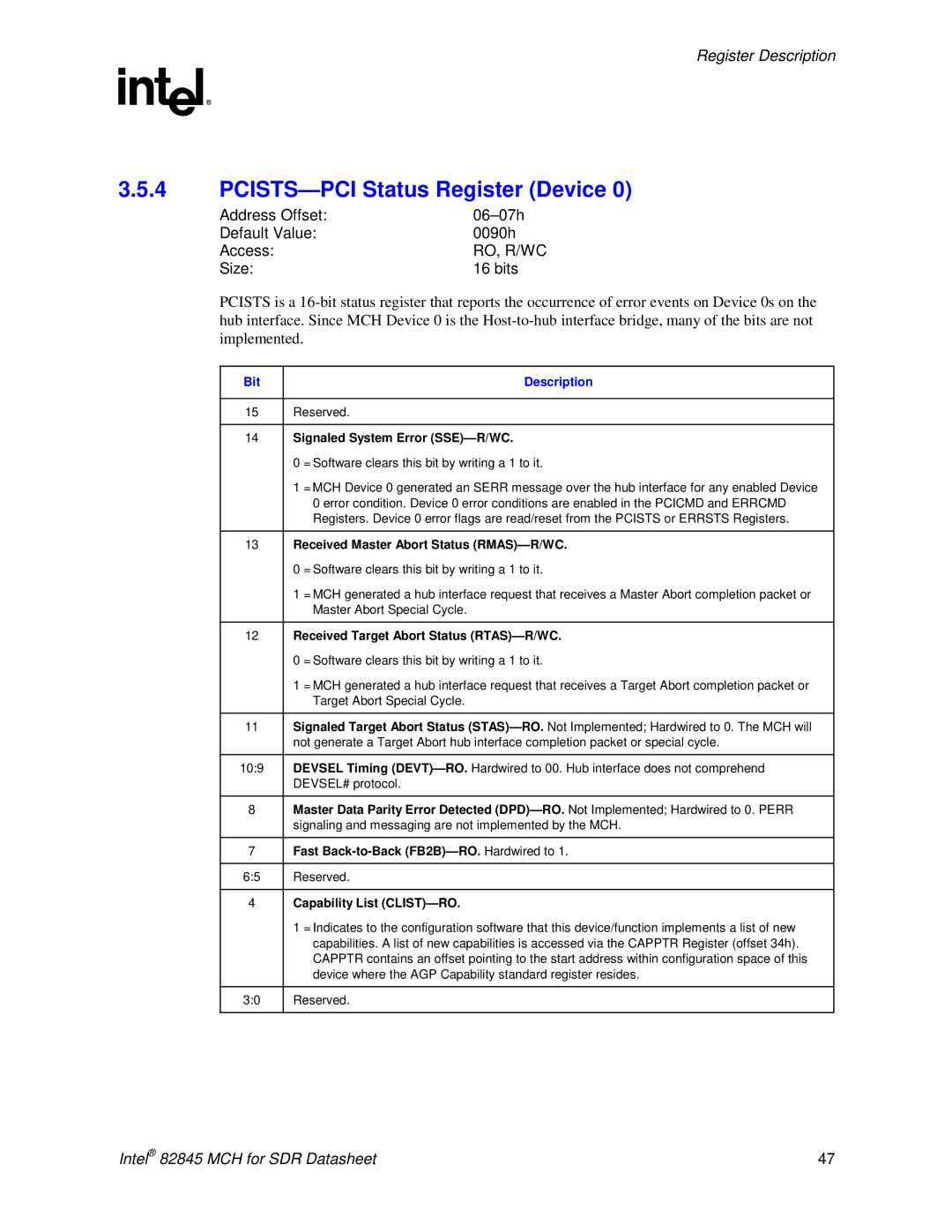

3.5.4PCISTS—PCI Status Register (Device 0)

Address Offset: |

|

Default Value: | 0090h |

Access: | RO, R/WC |

Size: | 16 bits |

PCISTS is a

Bit |

| Description |

|

| |

15 | Reserved. | |

|

| |

14 | Signaled System Error | |

| 0 | = Software clears this bit by writing a 1 to it. |

| 1 | = MCH Device 0 generated an SERR message over the hub interface for any enabled Device |

|

| 0 error condition. Device 0 error conditions are enabled in the PCICMD and ERRCMD |

|

| Registers. Device 0 error flags are read/reset from the PCISTS or ERRSTS Registers. |

|

| |

13 | Received Master Abort Status | |

| 0 | = Software clears this bit by writing a 1 to it. |

| 1 | = MCH generated a hub interface request that receives a Master Abort completion packet or |

|

| Master Abort Special Cycle. |

|

| |

12 | Received Target Abort Status | |

| 0 | = Software clears this bit by writing a 1 to it. |

| 1 | = MCH generated a hub interface request that receives a Target Abort completion packet or |

|

| Target Abort Special Cycle. |

|

| |

11 | Signaled Target Abort Status | |

| not generate a Target Abort hub interface completion packet or special cycle. | |

|

| |

10:9 | DEVSEL Timing | |

| DEVSEL# protocol. | |

|

| |

8 | Master Data Parity Error Detected | |

| signaling and messaging are not implemented by the MCH. | |

|

| |

7 | Fast | |

|

| |

6:5 | Reserved. | |

|

| |

4 | Capability List | |

| 1 | = Indicates to the configuration software that this device/function implements a list of new |

|

| capabilities. A list of new capabilities is accessed via the CAPPTR Register (offset 34h). |

|

| CAPPTR contains an offset pointing to the start address within configuration space of this |

|

| device where the AGP Capability standard register resides. |

|

| |

3:0 | Reserved. | |

|

|

|

Intel® 82845 MCH for SDR Datasheet | 47 |