Register Description

R

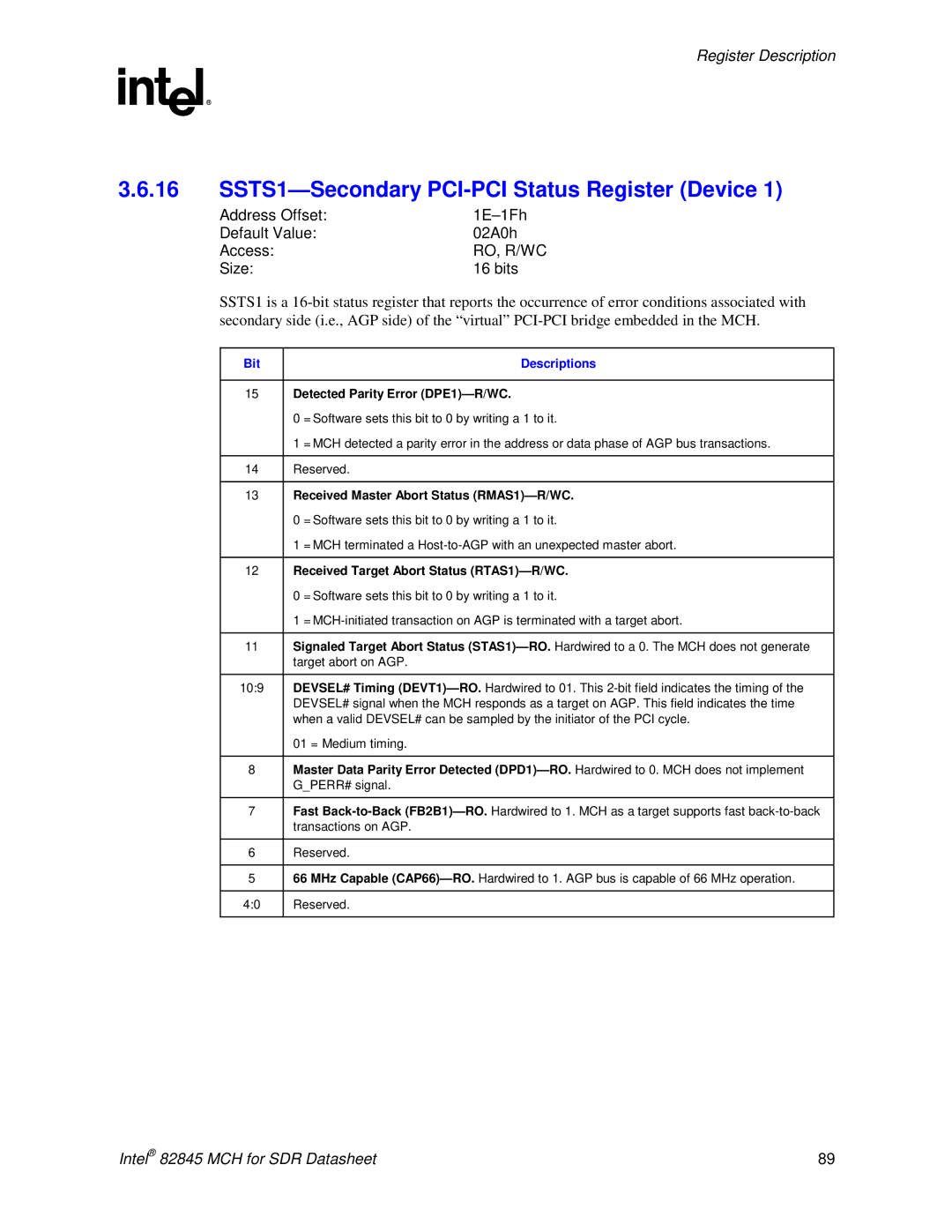

3.6.16SSTS1—Secondary PCI-PCI Status Register (Device 1)

Address Offset: |

|

Default Value: | 02A0h |

Access: | RO, R/WC |

Size: | 16 bits |

SSTS1 is a

Bit |

| Descriptions |

|

| |

15 | Detected Parity Error | |

| 0 | = Software sets this bit to 0 by writing a 1 to it. |

| 1 | = MCH detected a parity error in the address or data phase of AGP bus transactions. |

|

| |

14 | Reserved. | |

|

| |

13 | Received Master Abort Status | |

| 0 | = Software sets this bit to 0 by writing a 1 to it. |

| 1 | = MCH terminated a |

|

| |

12 | Received Target Abort Status | |

| 0 | = Software sets this bit to 0 by writing a 1 to it. |

| 1 | = |

|

| |

11 | Signaled Target Abort Status | |

| target abort on AGP. | |

|

| |

10:9 | DEVSEL# Timing | |

| DEVSEL# signal when the MCH responds as a target on AGP. This field indicates the time | |

| when a valid DEVSEL# can be sampled by the initiator of the PCI cycle. | |

| 01 = Medium timing. | |

|

| |

8 | Master Data Parity Error Detected | |

| G_PERR# signal. | |

|

| |

7 | Fast | |

| transactions on AGP. | |

|

| |

6 | Reserved. | |

|

| |

5 | 66 MHz Capable | |

|

| |

4:0 | Reserved. | |

|

|

|

Intel® 82845 MCH for SDR Datasheet | 89 |