Register Description

R

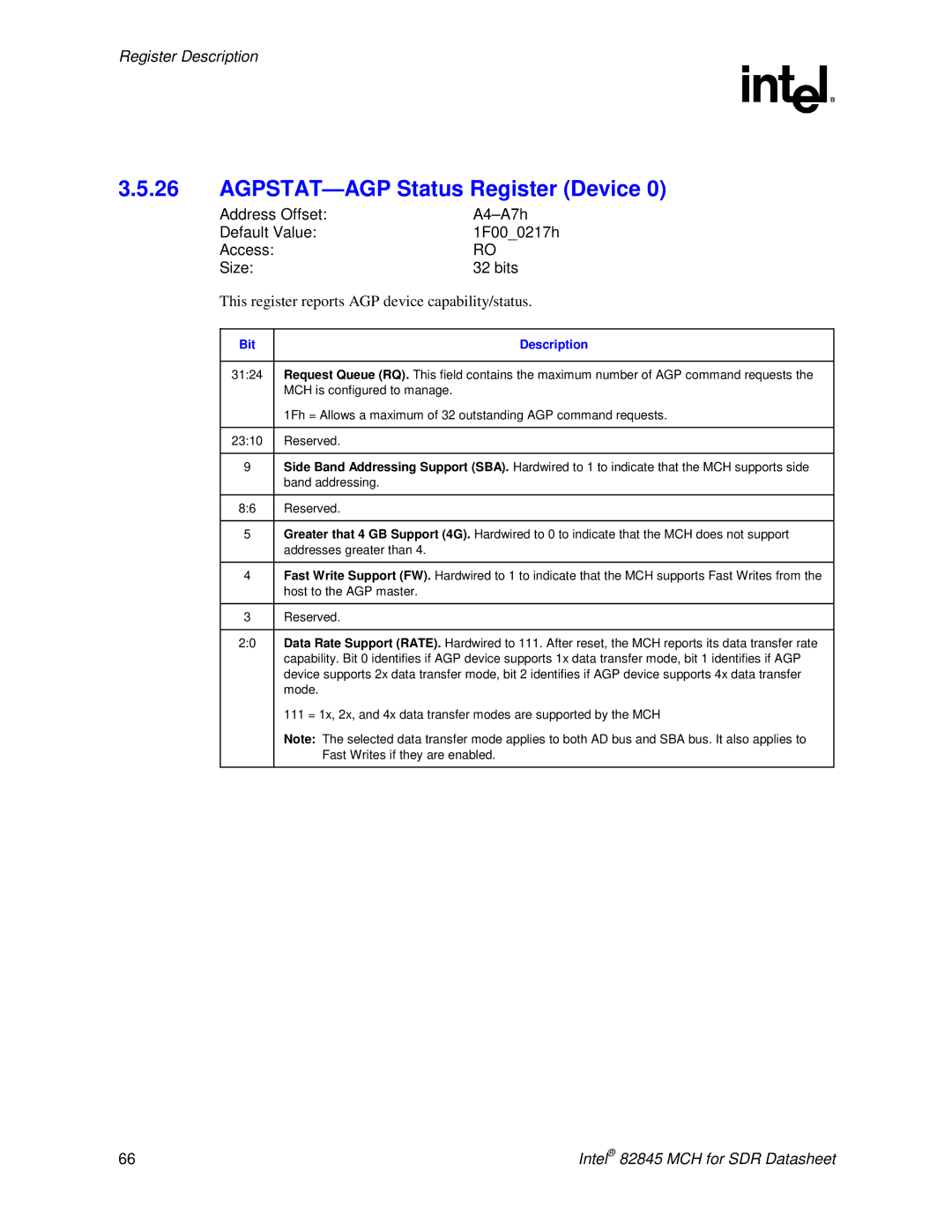

3.5.26AGPSTAT—AGP Status Register (Device 0)

Address Offset: | |

Default Value: | 1F00_0217h |

Access: | RO |

Size: | 32 bits |

This register reports AGP device capability/status.

Bit | Description |

|

|

31:24 | Request Queue (RQ). This field contains the maximum number of AGP command requests the |

| MCH is configured to manage. |

| 1Fh = Allows a maximum of 32 outstanding AGP command requests. |

|

|

23:10 | Reserved. |

|

|

9 | Side Band Addressing Support (SBA). Hardwired to 1 to indicate that the MCH supports side |

| band addressing. |

|

|

8:6 | Reserved. |

|

|

5 | Greater that 4 GB Support (4G). Hardwired to 0 to indicate that the MCH does not support |

| addresses greater than 4. |

|

|

4 | Fast Write Support (FW). Hardwired to 1 to indicate that the MCH supports Fast Writes from the |

| host to the AGP master. |

|

|

3 | Reserved. |

|

|

2:0 | Data Rate Support (RATE). Hardwired to 111. After reset, the MCH reports its data transfer rate |

| capability. Bit 0 identifies if AGP device supports 1x data transfer mode, bit 1 identifies if AGP |

| device supports 2x data transfer mode, bit 2 identifies if AGP device supports 4x data transfer |

| mode. |

| 111 = 1x, 2x, and 4x data transfer modes are supported by the MCH |

| Note: The selected data transfer mode applies to both AD bus and SBA bus. It also applies to |

| Fast Writes if they are enabled. |

|

|

66 | Intel® 82845 MCH for SDR Datasheet |