Register Description

R

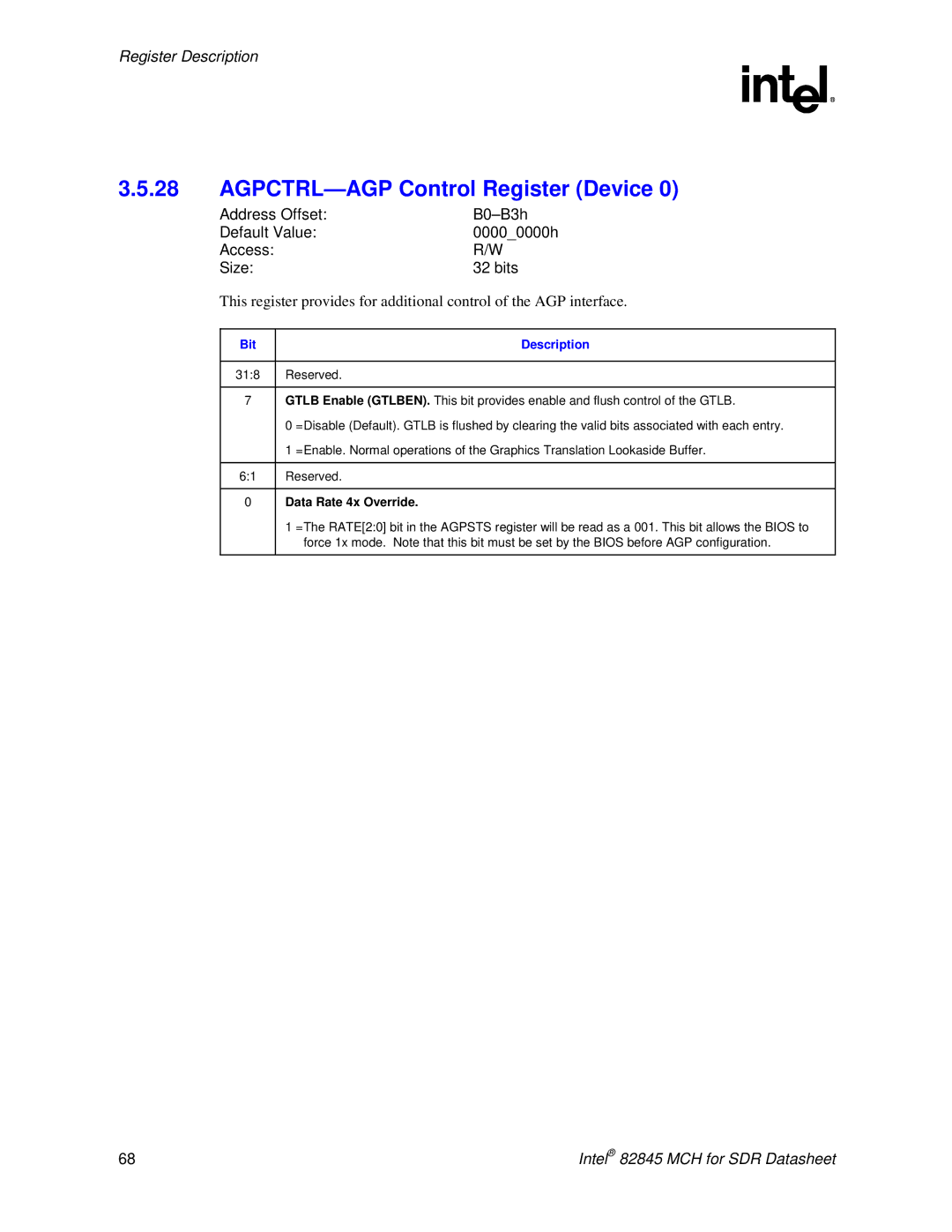

3.5.28AGPCTRL—AGP Control Register (Device 0)

Address Offset: | |

Default Value: | 0000_0000h |

Access: | R/W |

Size: | 32 bits |

This register provides for additional control of the AGP interface.

Bit |

| Description |

|

| |

31:8 | Reserved. | |

|

| |

7 | GTLB Enable (GTLBEN). This bit provides enable and flush control of the GTLB. | |

| 0 | =Disable (Default). GTLB is flushed by clearing the valid bits associated with each entry. |

| 1 | =Enable. Normal operations of the Graphics Translation Lookaside Buffer. |

|

| |

6:1 | Reserved. | |

|

| |

0 | Data Rate 4x Override. | |

| 1 | =The RATE[2:0] bit in the AGPSTS register will be read as a 001. This bit allows the BIOS to |

|

| force 1x mode. Note that this bit must be set by the BIOS before AGP configuration. |

|

|

|

68 | Intel® 82845 MCH for SDR Datasheet |