Register Description

R

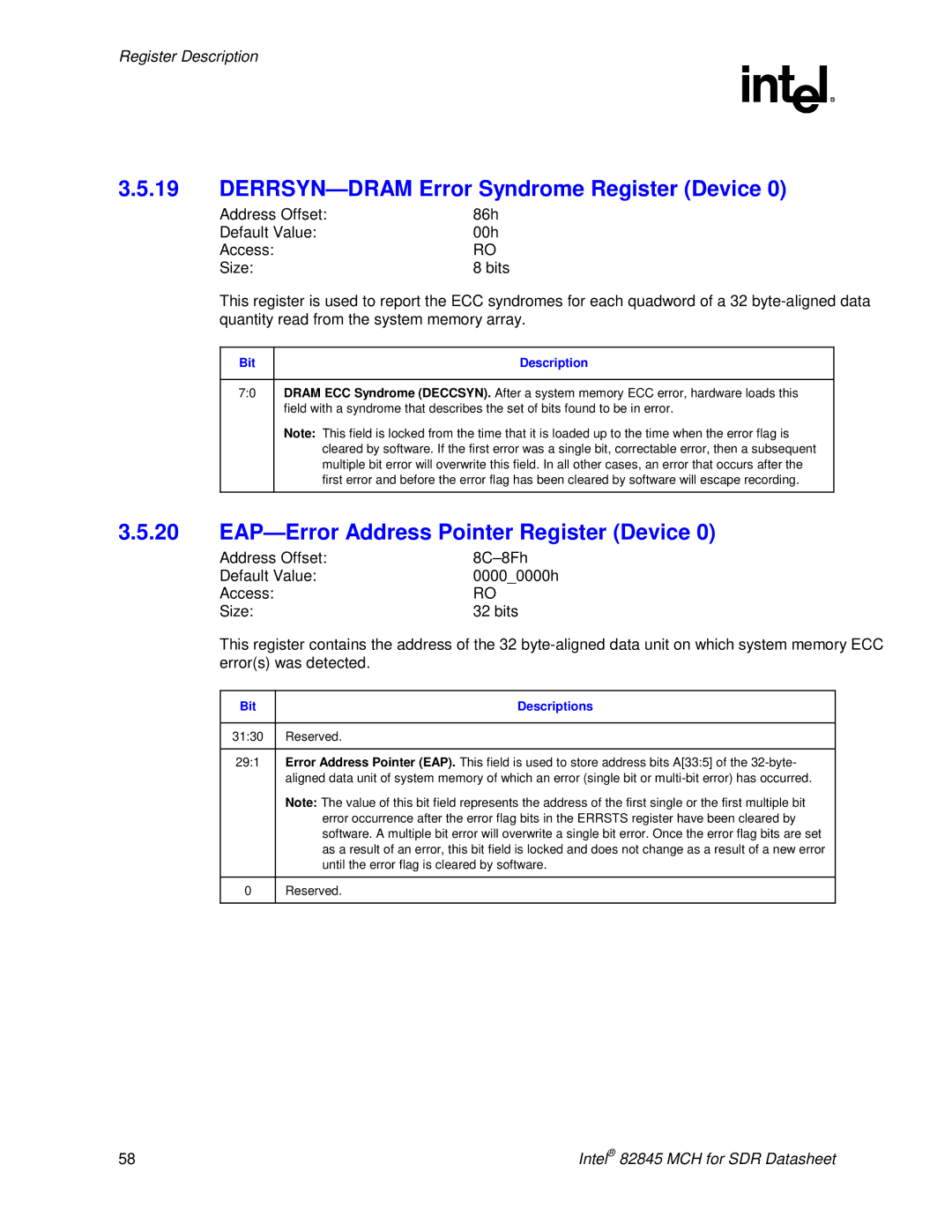

3.5.19DERRSYN—DRAM Error Syndrome Register (Device 0)

Address Offset: | 86h |

Default Value: | 00h |

Access: | RO |

Size: | 8 bits |

This register is used to report the ECC syndromes for each quadword of a 32

Bit | Description |

|

|

7:0 | DRAM ECC Syndrome (DECCSYN). After a system memory ECC error, hardware loads this |

| field with a syndrome that describes the set of bits found to be in error. |

| Note: This field is locked from the time that it is loaded up to the time when the error flag is |

| cleared by software. If the first error was a single bit, correctable error, then a subsequent |

| multiple bit error will overwrite this field. In all other cases, an error that occurs after the |

| first error and before the error flag has been cleared by software will escape recording. |

|

|

3.5.20EAP—Error Address Pointer Register (Device 0)

Address Offset: | |

Default Value: | 0000_0000h |

Access: | RO |

Size: | 32 bits |

This register contains the address of the 32

Bit | Descriptions |

|

|

31:30 | Reserved. |

|

|

29:1 | Error Address Pointer (EAP). This field is used to store address bits A[33:5] of the |

| aligned data unit of system memory of which an error (single bit or |

| Note: The value of this bit field represents the address of the first single or the first multiple bit |

| error occurrence after the error flag bits in the ERRSTS register have been cleared by |

| software. A multiple bit error will overwrite a single bit error. Once the error flag bits are set |

| as a result of an error, this bit field is locked and does not change as a result of a new error |

| until the error flag is cleared by software. |

|

|

0 | Reserved. |

|

|

58 | Intel® 82845 MCH for SDR Datasheet |