Introduction

R

1.4.3System Memory Interface

The MCH directly supports one channel of PC133 SDRAM. The memory interface supports Single Data Rate (SDR) devices with densities of 64 Mb, 128 Mb, 256 Mb, and 512 Mb technology. The memory interface also supports variable page sizes of 2 KB, 4 KB, 8 KB, and

16 KB. Page size is individually selected for every row and a maximum of 8 pages per DIMM may be opened simultaneously.

The MCH supports a maximum of 3

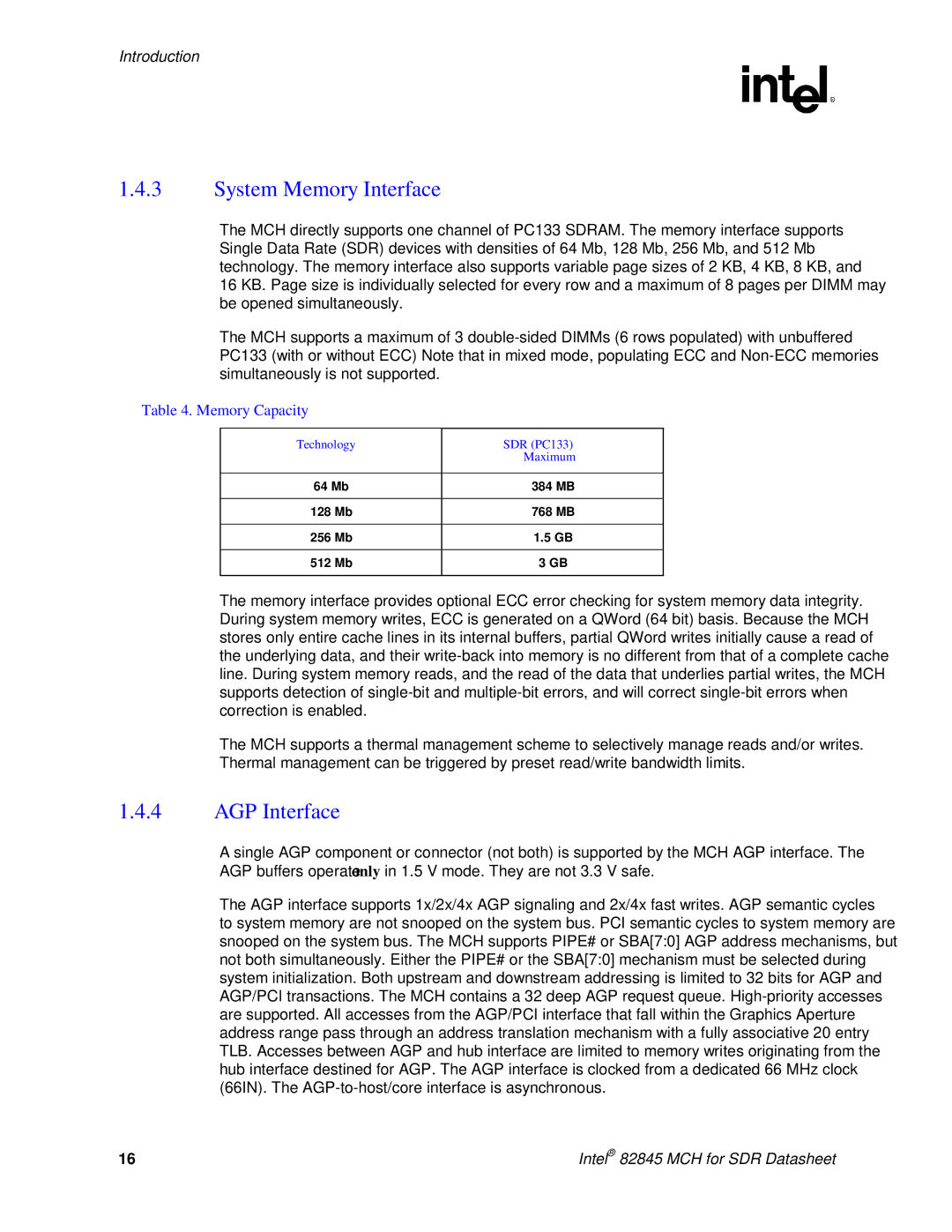

Table 4. Memory Capacity

Technology | SDR (PC133) |

| Maximum |

|

|

64 Mb | 384 MB |

|

|

128 Mb | 768 MB |

|

|

256 Mb | 1.5 GB |

|

|

512 Mb | 3 GB |

|

|

The memory interface provides optional ECC error checking for system memory data integrity. During system memory writes, ECC is generated on a QWord (64 bit) basis. Because the MCH stores only entire cache lines in its internal buffers, partial QWord writes initially cause a read of the underlying data, and their

The MCH supports a thermal management scheme to selectively manage reads and/or writes. Thermal management can be triggered by preset read/write bandwidth limits.

1.4.4AGP Interface

A single AGP component or connector (not both) is supported by the MCH AGP interface. The AGP buffers operate only in 1.5 V mode. They are not 3.3 V safe.

The AGP interface supports 1x/2x/4x AGP signaling and 2x/4x fast writes. AGP semantic cycles to system memory are not snooped on the system bus. PCI semantic cycles to system memory are snooped on the system bus. The MCH supports PIPE# or SBA[7:0] AGP address mechanisms, but not both simultaneously. Either the PIPE# or the SBA[7:0] mechanism must be selected during system initialization. Both upstream and downstream addressing is limited to 32 bits for AGP and AGP/PCI transactions. The MCH contains a 32 deep AGP request queue.

16 | Intel® 82845 MCH for SDR Datasheet |