Register Description

R

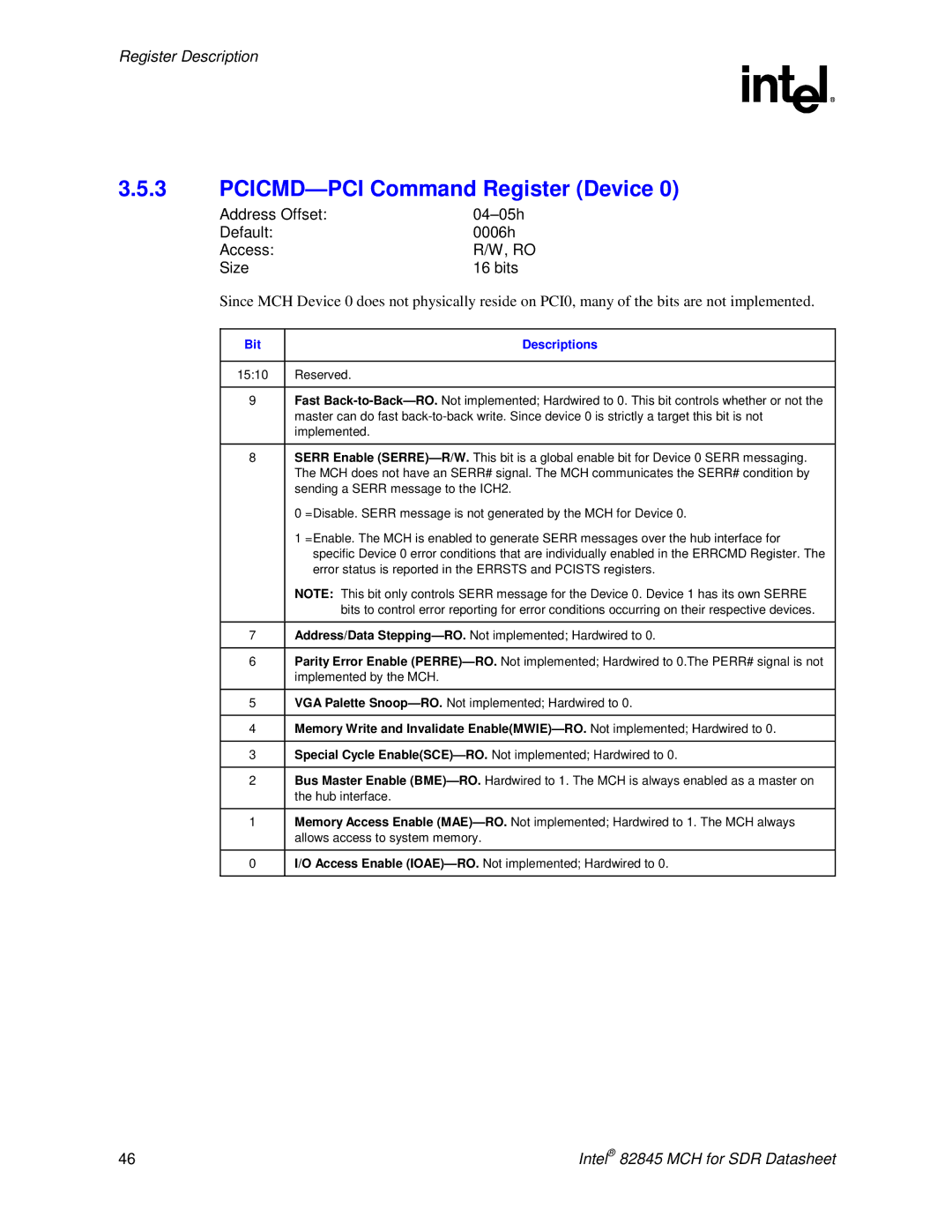

3.5.3PCICMD—PCI Command Register (Device 0)

Address Offset: |

|

Default: | 0006h |

Access: | R/W, RO |

Size | 16 bits |

Since MCH Device 0 does not physically reside on PCI0, many of the bits are not implemented.

Bit | Descriptions |

|

|

15:10 | Reserved. |

|

|

9 | Fast |

| master can do fast |

| implemented. |

|

|

8 | SERR Enable |

| The MCH does not have an SERR# signal. The MCH communicates the SERR# condition by |

| sending a SERR message to the ICH2. |

| 0 =Disable. SERR message is not generated by the MCH for Device 0. |

| 1 =Enable. The MCH is enabled to generate SERR messages over the hub interface for |

| specific Device 0 error conditions that are individually enabled in the ERRCMD Register. The |

| error status is reported in the ERRSTS and PCISTS registers. |

| NOTE: This bit only controls SERR message for the Device 0. Device 1 has its own SERRE |

| bits to control error reporting for error conditions occurring on their respective devices. |

|

|

7 | Address/Data |

|

|

6 | Parity Error Enable |

| implemented by the MCH. |

|

|

5 | VGA Palette |

|

|

4 | Memory Write and Invalidate |

|

|

3 | Special Cycle |

|

|

2 | Bus Master Enable |

| the hub interface. |

|

|

1 | Memory Access Enable |

| allows access to system memory. |

|

|

0 | I/O Access Enable |

|

|

46 | Intel® 82845 MCH for SDR Datasheet |