Register Description

R

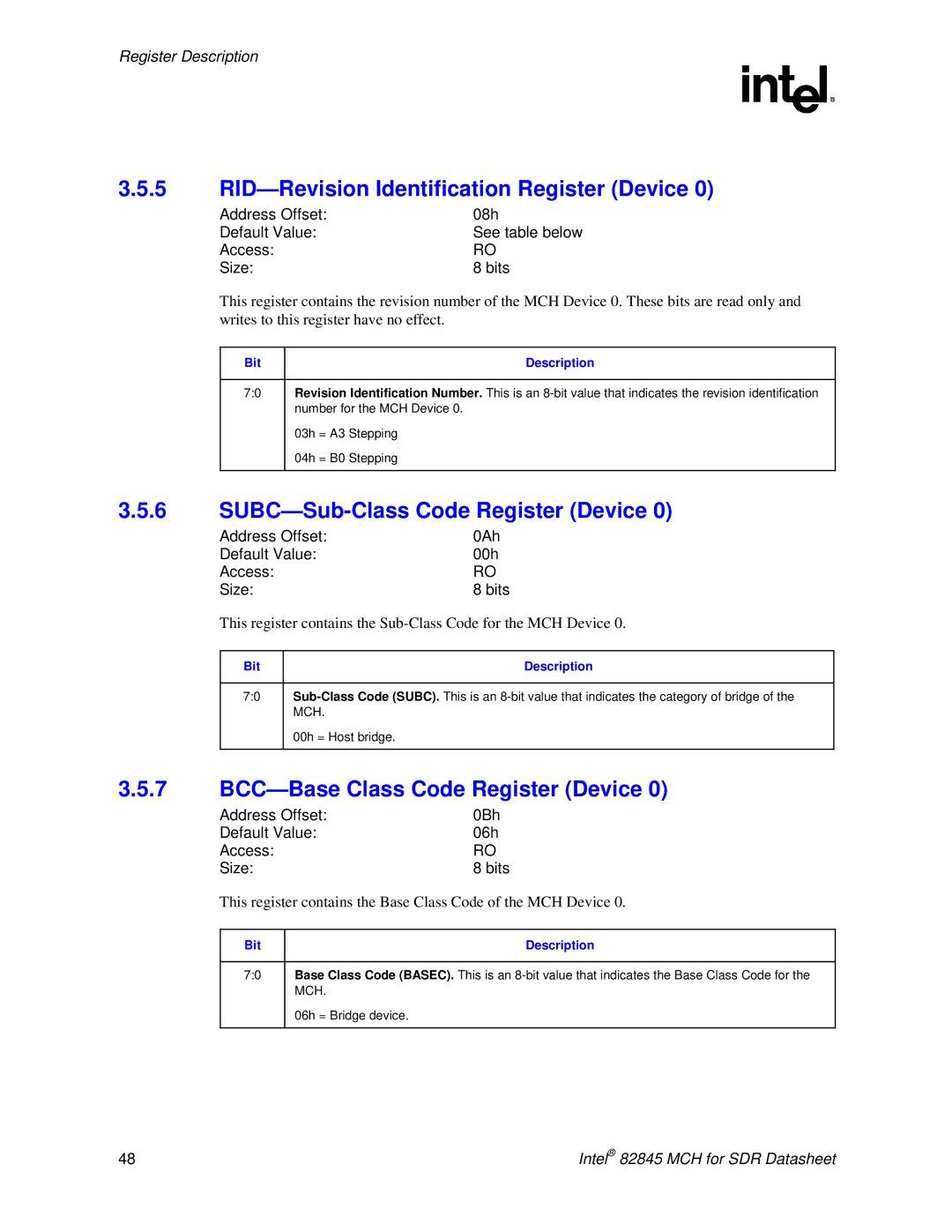

3.5.5RID—Revision Identification Register (Device 0)

Address Offset: | 08h |

Default Value: | See table below |

Access: | RO |

Size: | 8 bits |

This register contains the revision number of the MCH Device 0. These bits are read only and writes to this register have no effect.

Bit | Description |

|

|

7:0 | Revision Identification Number. This is an |

| number for the MCH Device 0. |

| 03h = A3 Stepping |

| 04h = B0 Stepping |

|

|

3.5.6SUBC—Sub-Class Code Register (Device 0)

Address Offset: | 0Ah |

Default Value: | 00h |

Access: | RO |

Size: | 8 bits |

This register contains the

Bit | Description |

|

|

7:0 | |

| MCH. |

| 00h = Host bridge. |

|

|

3.5.7BCC—Base Class Code Register (Device 0)

Address Offset: | 0Bh |

Default Value: | 06h |

Access: | RO |

Size: | 8 bits |

This register contains the Base Class Code of the MCH Device 0.

Bit | Description |

|

|

7:0 | Base Class Code (BASEC). This is an |

| MCH. |

| 06h = Bridge device. |

|

|

48 | Intel® 82845 MCH for SDR Datasheet |