Signal Description

R

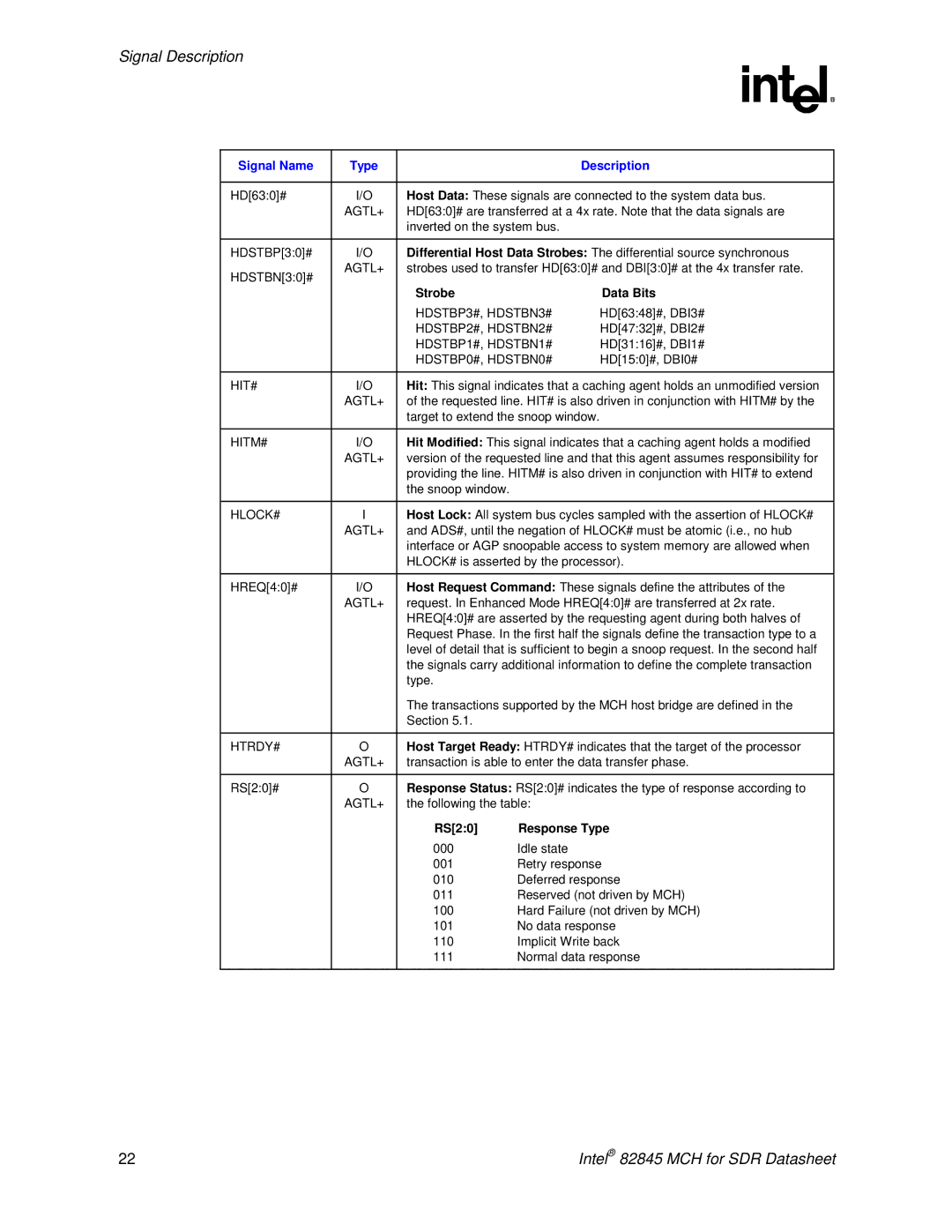

Signal Name | Type |

|

| Description |

|

|

| ||

HD[63:0]# | I/O | Host Data: These signals are connected to the system data bus. | ||

| AGTL+ | HD[63:0]# are transferred at a 4x rate. Note that the data signals are | ||

|

| inverted on the system bus. |

| |

|

|

| ||

HDSTBP[3:0]# | I/O | Differential Host Data Strobes: The differential source synchronous | ||

HDSTBN[3:0]# | AGTL+ | strobes used to transfer HD[63:0]# and DBI[3:0]# at the 4x transfer rate. | ||

| Strobe |

| Data Bits | |

|

|

| ||

|

| HDSTBP3#, HDSTBN3# | HD[63:48]#, DBI3# | |

|

| HDSTBP2#, HDSTBN2# | HD[47:32]#, DBI2# | |

|

| HDSTBP1#, HDSTBN1# | HD[31:16]#, DBI1# | |

|

| HDSTBP0#, HDSTBN0# | HD[15:0]#, DBI0# | |

|

|

| ||

HIT# | I/O | Hit: This signal indicates that a caching agent holds an unmodified version | ||

| AGTL+ | of the requested line. HIT# is also driven in conjunction with HITM# by the | ||

|

| target to extend the snoop window. | ||

|

|

| ||

HITM# | I/O | Hit Modified: This signal indicates that a caching agent holds a modified | ||

| AGTL+ | version of the requested line and that this agent assumes responsibility for | ||

|

| providing the line. HITM# is also driven in conjunction with HIT# to extend | ||

|

| the snoop window. |

|

|

|

|

| ||

HLOCK# | I | Host Lock: All system bus cycles sampled with the assertion of HLOCK# | ||

| AGTL+ | and ADS#, until the negation of HLOCK# must be atomic (i.e., no hub | ||

|

| interface or AGP snoopable access to system memory are allowed when | ||

|

| HLOCK# is asserted by the processor). | ||

|

|

| ||

HREQ[4:0]# | I/O | Host Request Command: These signals define the attributes of the | ||

| AGTL+ | request. In Enhanced Mode HREQ[4:0]# are transferred at 2x rate. | ||

|

| HREQ[4:0]# are asserted by the requesting agent during both halves of | ||

|

| Request Phase. In the first half the signals define the transaction type to a | ||

|

| level of detail that is sufficient to begin a snoop request. In the second half | ||

|

| the signals carry additional information to define the complete transaction | ||

|

| type. |

|

|

|

| The transactions supported by the MCH host bridge are defined in the | ||

|

| Section 5.1. |

|

|

|

|

| ||

HTRDY# | O | Host Target Ready: HTRDY# indicates that the target of the processor | ||

| AGTL+ | transaction is able to enter the data transfer phase. | ||

|

|

| ||

RS[2:0]# | O | Response Status: RS[2:0]# indicates the type of response according to | ||

| AGTL+ | the following the table: |

| |

|

| RS[2:0] | Response Type | |

|

| 000 | Idle state |

|

|

| 001 | Retry response | |

|

| 010 | Deferred response | |

|

| 011 | Reserved (not driven by MCH) | |

|

| 100 | Hard Failure (not driven by MCH) | |

|

| 101 | No data response | |

|

| 110 | Implicit Write back | |

|

| 111 | Normal data response | |

|

|

|

|

|

22 | Intel® 82845 MCH for SDR Datasheet |