Register Description

R

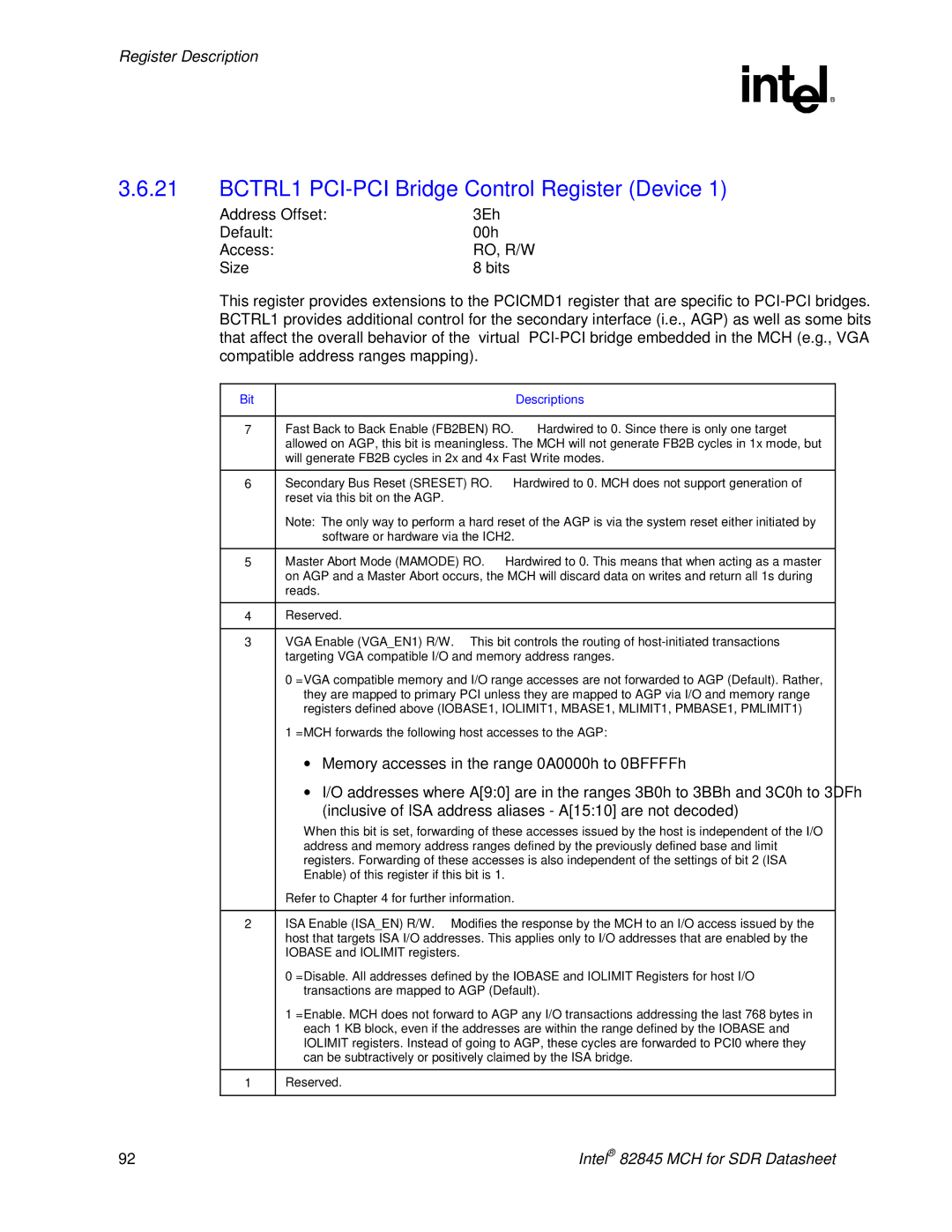

3.6.21BCTRL1—PCI-PCI Bridge Control Register (Device 1)

Address Offset: | 3Eh |

Default: | 00h |

Access: | RO, R/W |

Size | 8 bits |

This register provides extensions to the PCICMD1 register that are specific to

| Bit | Descriptions |

|

|

|

| 7 | Fast Back to Back Enable |

|

| allowed on AGP, this bit is meaningless. The MCH will not generate FB2B cycles in 1x mode, but |

|

| will generate FB2B cycles in 2x and 4x Fast Write modes. |

|

|

|

| 6 | Secondary Bus Reset |

|

| reset via this bit on the AGP. |

|

| Note: The only way to perform a hard reset of the AGP is via the system reset either initiated by |

|

| software or hardware via the ICH2. |

|

|

|

| 5 | Master Abort Mode |

|

| on AGP and a Master Abort occurs, the MCH will discard data on writes and return all 1s during |

|

| reads. |

|

|

|

| 4 | Reserved. |

|

|

|

| 3 | VGA Enable |

|

| targeting VGA compatible I/O and memory address ranges. |

|

| 0 =VGA compatible memory and I/O range accesses are not forwarded to AGP (Default). Rather, |

|

| they are mapped to primary PCI unless they are mapped to AGP via I/O and memory range |

|

| registers defined above (IOBASE1, IOLIMIT1, MBASE1, MLIMIT1, PMBASE1, PMLIMIT1) |

|

| 1 =MCH forwards the following host accesses to the AGP: |

|

| • Memory accesses in the range 0A0000h to 0BFFFFh |

|

| • I/O addresses where A[9:0] are in the ranges 3B0h to 3BBh and 3C0h to 3DFh |

|

| (inclusive of ISA address aliases - A[15:10] are not decoded) |

|

| When this bit is set, forwarding of these accesses issued by the host is independent of the I/O |

|

| address and memory address ranges defined by the previously defined base and limit |

|

| registers. Forwarding of these accesses is also independent of the settings of bit 2 (ISA |

|

| Enable) of this register if this bit is 1. |

|

| Refer to Chapter 4 for further information. |

|

|

|

| 2 | ISA Enable |

|

| host that targets ISA I/O addresses. This applies only to I/O addresses that are enabled by the |

|

| IOBASE and IOLIMIT registers. |

|

| 0 =Disable. All addresses defined by the IOBASE and IOLIMIT Registers for host I/O |

|

| transactions are mapped to AGP (Default). |

|

| 1 =Enable. MCH does not forward to AGP any I/O transactions addressing the last 768 bytes in |

|

| each 1 KB block, even if the addresses are within the range defined by the IOBASE and |

|

| IOLIMIT registers. Instead of going to AGP, these cycles are forwarded to PCI0 where they |

|

| can be subtractively or positively claimed by the ISA bridge. |

|

|

|

| 1 | Reserved. |

|

|

|

92 |

| Intel® 82845 MCH for SDR Datasheet |