Register Description

R

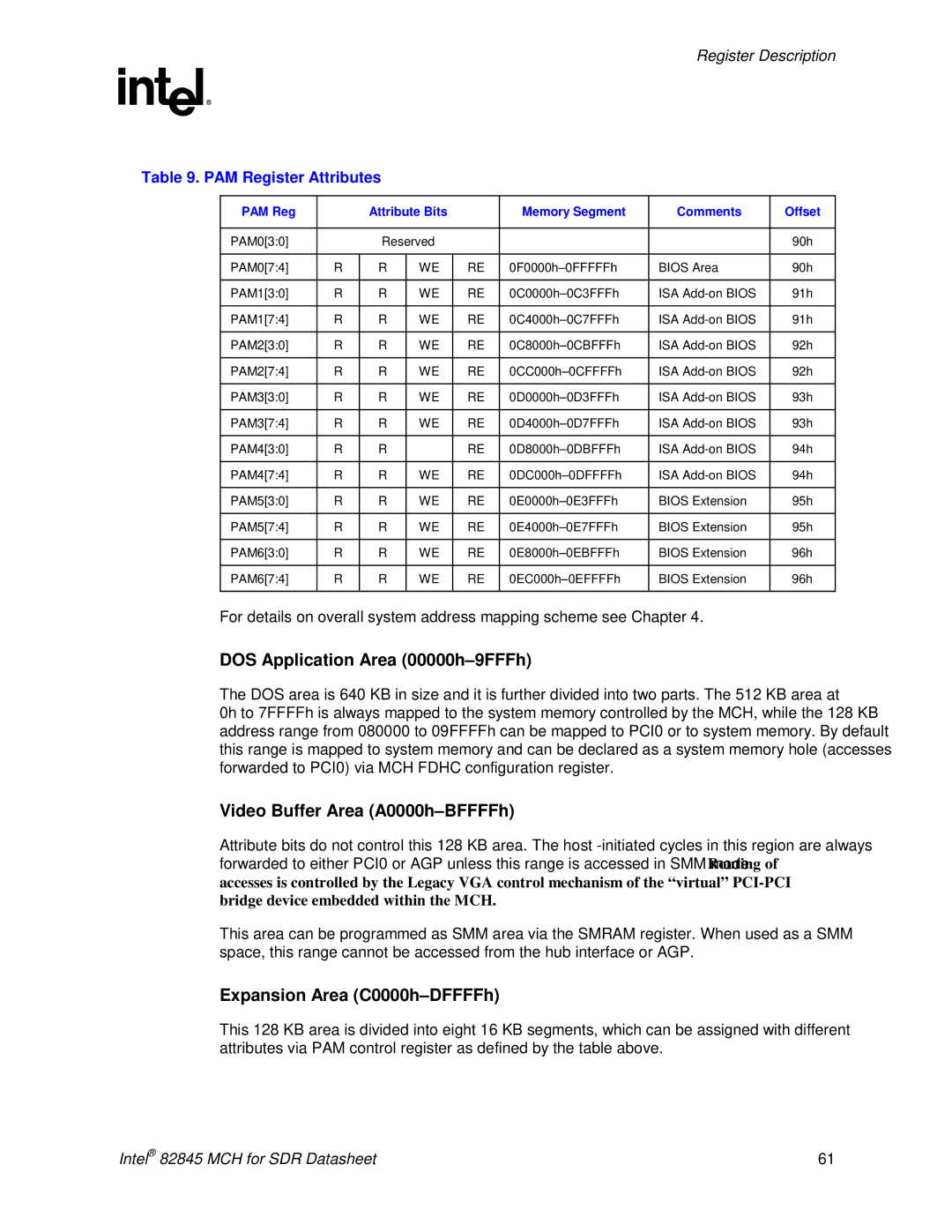

Table 9. PAM Register Attributes

PAM Reg |

| Attribute Bits |

| Memory Segment | Comments | Offset | |

|

|

|

|

|

|

|

|

PAM0[3:0] |

| Reserved |

|

|

| 90h | |

|

|

|

|

|

|

|

|

PAM0[7:4] | R | R | WE | RE | BIOS Area | 90h | |

|

|

|

|

|

|

|

|

PAM1[3:0] | R | R | WE | RE | ISA | 91h | |

|

|

|

|

|

|

|

|

PAM1[7:4] | R | R | WE | RE | ISA | 91h | |

|

|

|

|

|

|

|

|

PAM2[3:0] | R | R | WE | RE | ISA | 92h | |

|

|

|

|

|

|

|

|

PAM2[7:4] | R | R | WE | RE | ISA | 92h | |

|

|

|

|

|

|

|

|

PAM3[3:0] | R | R | WE | RE | ISA | 93h | |

|

|

|

|

|

|

|

|

PAM3[7:4] | R | R | WE | RE | ISA | 93h | |

|

|

|

|

|

|

|

|

PAM4[3:0] | R | R |

| RE | ISA | 94h | |

|

|

|

|

|

|

|

|

PAM4[7:4] | R | R | WE | RE | ISA | 94h | |

|

|

|

|

|

|

|

|

PAM5[3:0] | R | R | WE | RE | BIOS Extension | 95h | |

|

|

|

|

|

|

|

|

PAM5[7:4] | R | R | WE | RE | BIOS Extension | 95h | |

|

|

|

|

|

|

|

|

PAM6[3:0] | R | R | WE | RE | BIOS Extension | 96h | |

|

|

|

|

|

|

|

|

PAM6[7:4] | R | R | WE | RE | BIOS Extension | 96h | |

|

|

|

|

|

|

|

|

For details on overall system address mapping scheme see Chapter 4.

DOS Application Area (00000h–9FFFh)

The DOS area is 640 KB in size and it is further divided into two parts. The 512 KB area at

0h to 7FFFFh is always mapped to the system memory controlled by the MCH, while the 128 KB address range from 080000 to 09FFFFh can be mapped to PCI0 or to system memory. By default this range is mapped to system memory and can be declared as a system memory hole (accesses forwarded to PCI0) via MCH FDHC configuration register.

Video Buffer Area (A0000h–BFFFFh)

Attribute bits do not control this 128 KB area. The host

This area can be programmed as SMM area via the SMRAM register. When used as a SMM space, this range cannot be accessed from the hub interface or AGP.

Expansion Area (C0000h–DFFFFh)

This 128 KB area is divided into eight 16 KB segments, which can be assigned with different attributes via PAM control register as defined by the table above.

Intel® 82845 MCH for SDR Datasheet | 61 |