Register Description

R

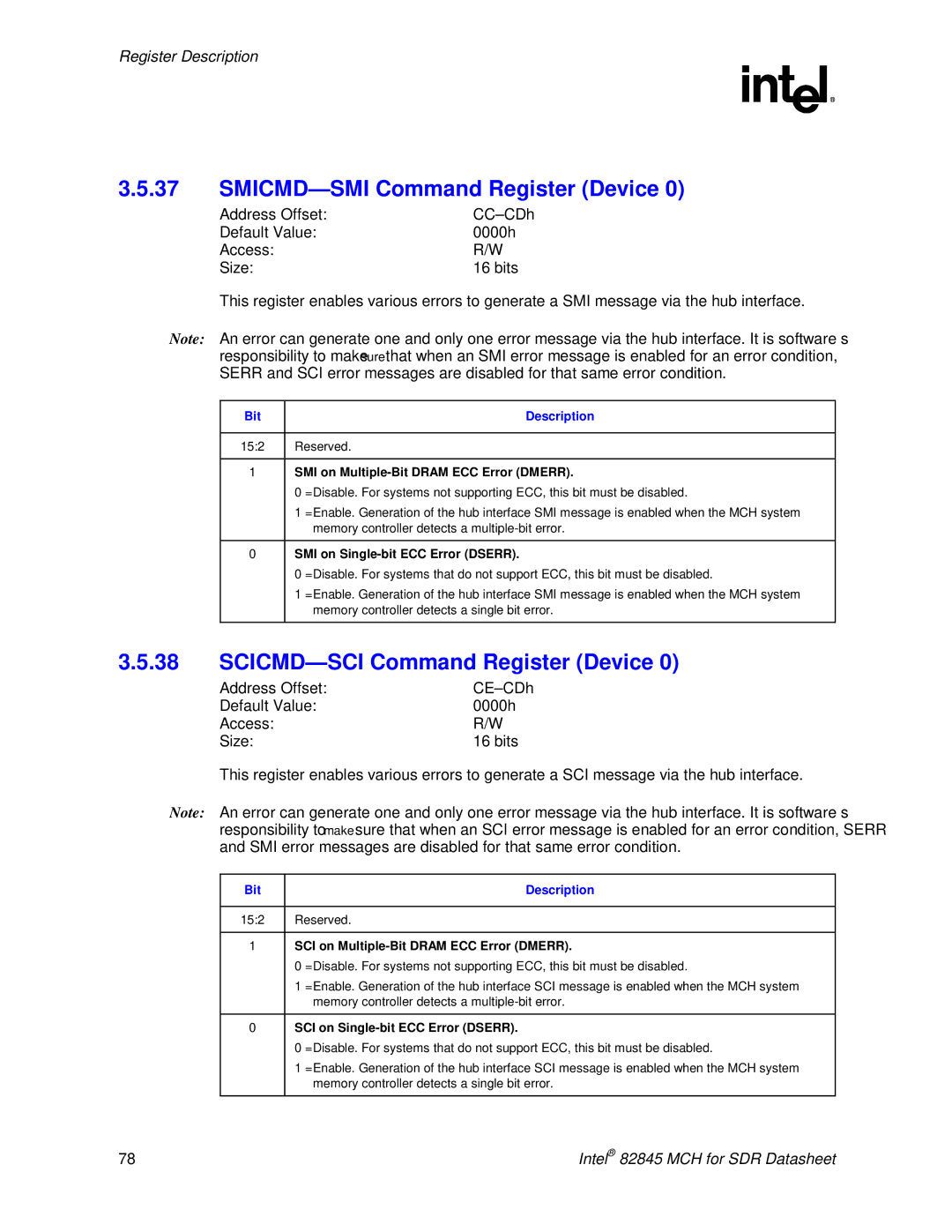

3.5.37SMICMD—SMI Command Register (Device 0)

Address Offset: |

|

Default Value: | 0000h |

Access: | R/W |

Size: | 16 bits |

This register enables various errors to generate a SMI message via the hub interface.

Note: An error can generate one and only one error message via the hub interface. It is software’s responsibility to make sure that when an SMI error message is enabled for an error condition, SERR and SCI error messages are disabled for that same error condition.

Bit |

| Description |

|

| |

15:2 | Reserved. | |

|

| |

1 | SMI on | |

| 0 | =Disable. For systems not supporting ECC, this bit must be disabled. |

| 1 | =Enable. Generation of the hub interface SMI message is enabled when the MCH system |

|

| memory controller detects a |

|

| |

0 | SMI on | |

| 0 | =Disable. For systems that do not support ECC, this bit must be disabled. |

| 1 | =Enable. Generation of the hub interface SMI message is enabled when the MCH system |

|

| memory controller detects a single bit error. |

|

|

|

3.5.38SCICMD—SCI Command Register (Device 0)

Address Offset: |

|

Default Value: | 0000h |

Access: | R/W |

Size: | 16 bits |

This register enables various errors to generate a SCI message via the hub interface.

Note: An error can generate one and only one error message via the hub interface. It is software’s responsibility to make sure that when an SCI error message is enabled for an error condition, SERR and SMI error messages are disabled for that same error condition.

Bit |

| Description |

|

| |

15:2 | Reserved. | |

|

| |

1 | SCI on | |

| 0 | =Disable. For systems not supporting ECC, this bit must be disabled. |

| 1 | =Enable. Generation of the hub interface SCI message is enabled when the MCH system |

|

| memory controller detects a |

|

| |

0 | SCI on | |

| 0 | =Disable. For systems that do not support ECC, this bit must be disabled. |

| 1 | =Enable. Generation of the hub interface SCI message is enabled when the MCH system |

|

| memory controller detects a single bit error. |

|

|

|

78 | Intel® 82845 MCH for SDR Datasheet |