Register Description

R

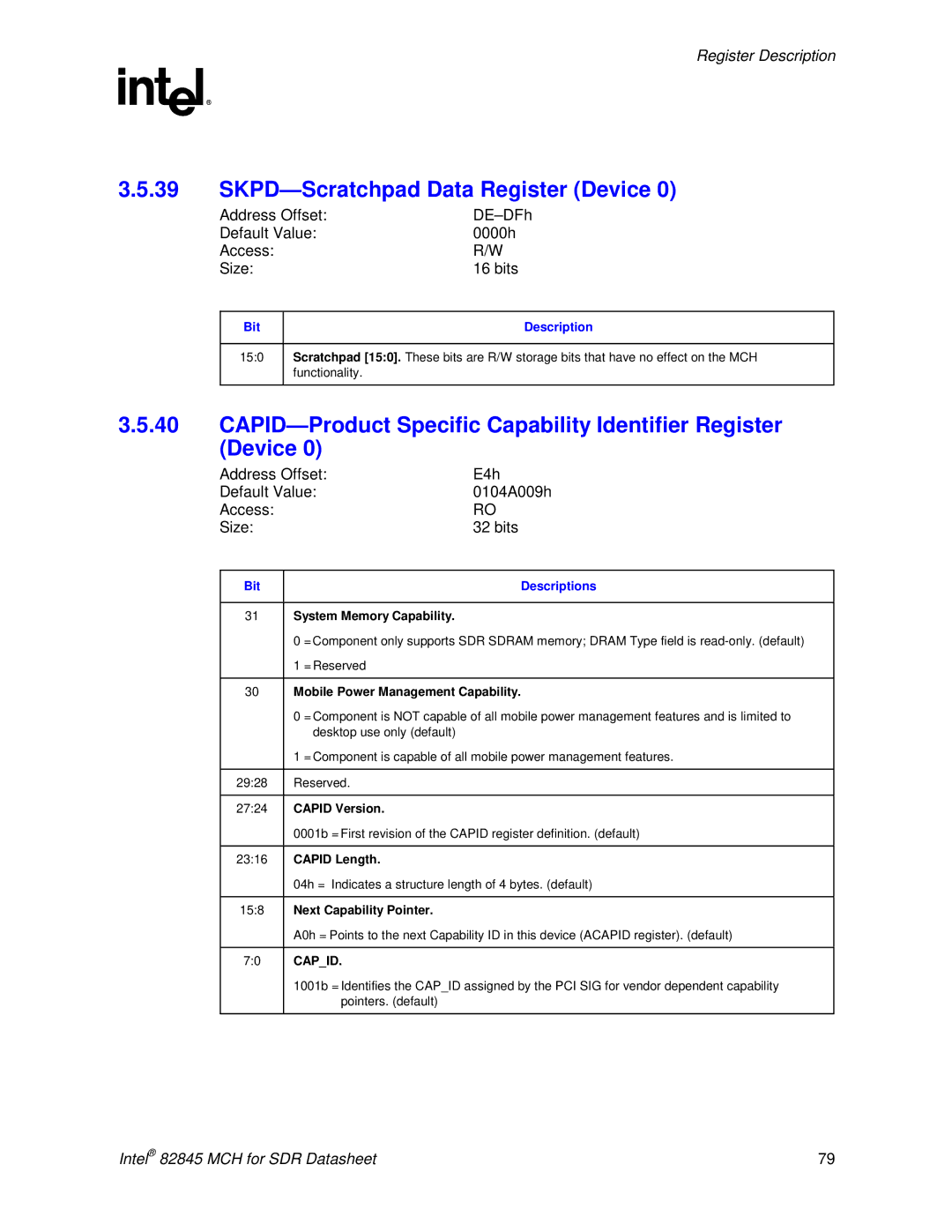

3.5.39SKPD—Scratchpad Data Register (Device 0)

Address Offset: |

| |

Default Value: | 0000h | |

Access: |

| R/W |

Size: |

| 16 bits |

|

|

|

Bit |

| Description |

|

| |

15:0 | Scratchpad [15:0]. These bits are R/W storage bits that have no effect on the MCH | |

| functionality. |

|

|

|

|

3.5.40

Address Offset: | E4h | |

Default Value: | 0104A009h | |

Access: |

| RO |

Size: |

| 32 bits |

|

|

|

Bit |

| Descriptions |

|

| |

31 | System Memory Capability. | |

| 0 = Component only supports SDR SDRAM memory; DRAM Type field is | |

| 1 = Reserved | |

|

| |

30 | Mobile Power Management Capability. | |

| 0 = Component is NOT capable of all mobile power management features and is limited to | |

| desktop use only (default) | |

| 1 = Component is capable of all mobile power management features. | |

|

| |

29:28 | Reserved. | |

|

| |

27:24 | CAPID Version. | |

| 0001b = First revision of the CAPID register definition. (default) | |

|

| |

23:16 | CAPID Length. | |

| 04h = | Indicates a structure length of 4 bytes. (default) |

|

| |

15:8 | Next Capability Pointer. | |

| A0h = Points to the next Capability ID in this device (ACAPID register). (default) | |

|

| |

7:0 | CAP_ID. | |

| 1001b = Identifies the CAP_ID assigned by the PCI SIG for vendor dependent capability | |

|

| pointers. (default) |

|

|

|

Intel® 82845 MCH for SDR Datasheet | 79 |