Register Description

R

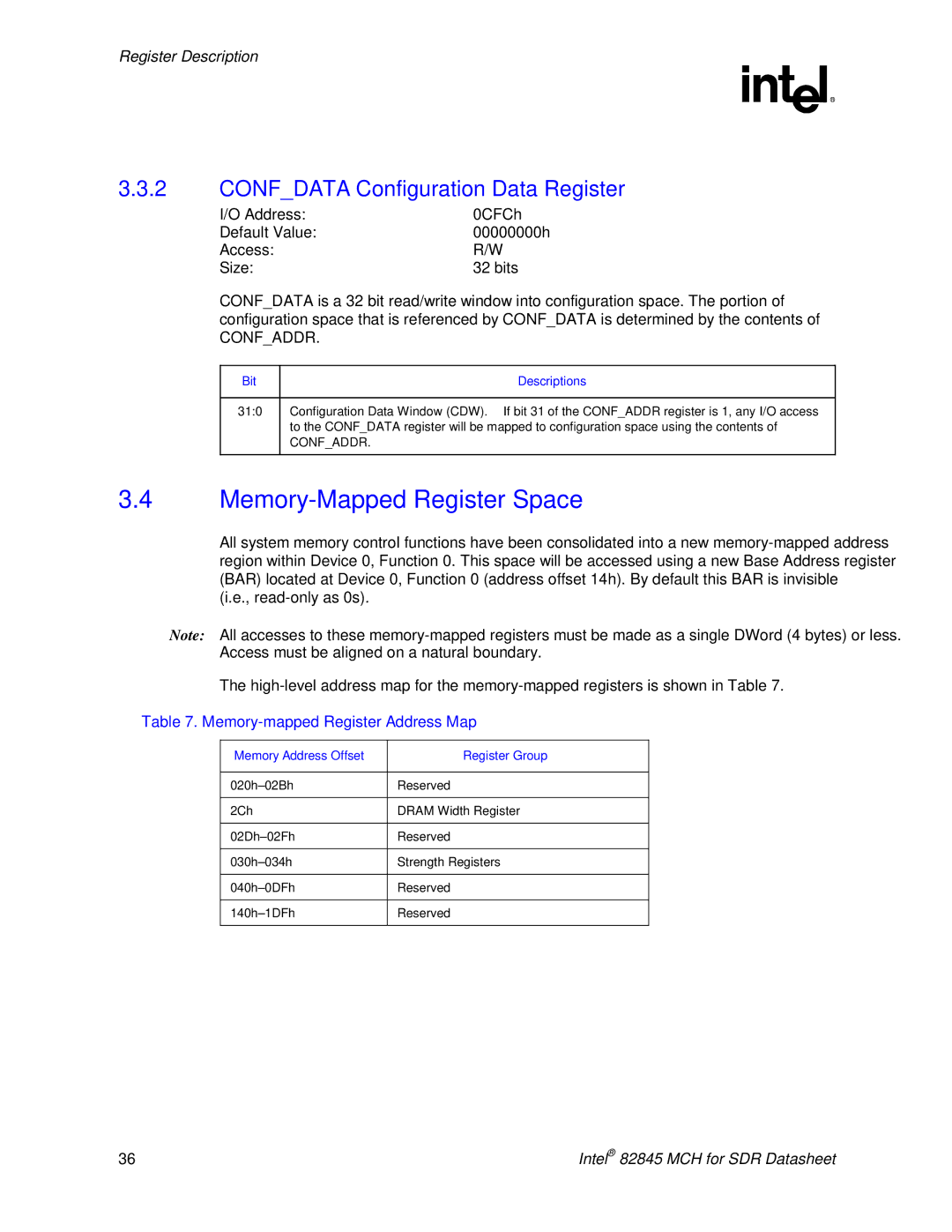

3.3.2CONF_DATA—Configuration Data Register

I/O Address: | 0CFCh |

Default Value: | 00000000h |

Access: | R/W |

Size: | 32 bits |

CONF_DATA is a 32 bit read/write window into configuration space. The portion of configuration space that is referenced by CONF_DATA is determined by the contents of CONF_ADDR.

Bit | Descriptions |

|

|

31:0 | Configuration Data Window (CDW). If bit 31 of the CONF_ADDR register is 1, any I/O access |

| to the CONF_DATA register will be mapped to configuration space using the contents of |

| CONF_ADDR. |

|

|

3.4Memory-Mapped Register Space

All system memory control functions have been consolidated into a new

Note: All accesses to these

The

Table 7. Memory-mapped Register Address Map

Memory Address Offset | Register Group |

|

|

Reserved | |

|

|

2Ch | DRAM Width Register |

|

|

Reserved | |

|

|

Strength Registers | |

|

|

Reserved | |

|

|

Reserved | |

|

|

36 | Intel® 82845 MCH for SDR Datasheet |