Register Description

R

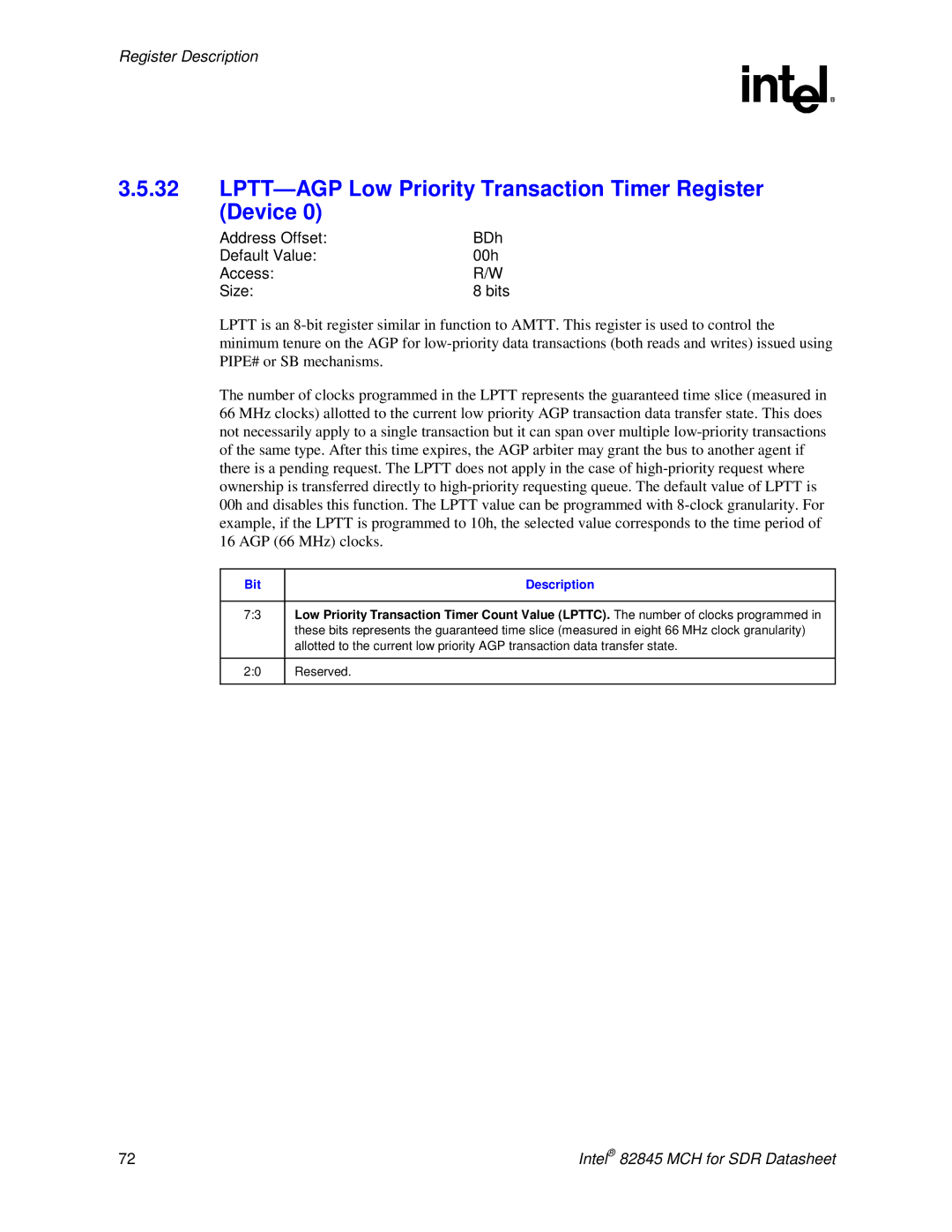

3.5.32LPTT—AGP Low Priority Transaction Timer Register (Device 0)

Address Offset: | BDh |

Default Value: | 00h |

Access: | R/W |

Size: | 8 bits |

LPTT is an

The number of clocks programmed in the LPTT represents the guaranteed time slice (measured in 66 MHz clocks) allotted to the current low priority AGP transaction data transfer state. This does not necessarily apply to a single transaction but it can span over multiple

Bit | Description |

|

|

7:3 | Low Priority Transaction Timer Count Value (LPTTC). The number of clocks programmed in |

| these bits represents the guaranteed time slice (measured in eight 66 MHz clock granularity) |

| allotted to the current low priority AGP transaction data transfer state. |

|

|

2:0 | Reserved. |

|

|

72 | Intel® 82845 MCH for SDR Datasheet |