Register Description

R

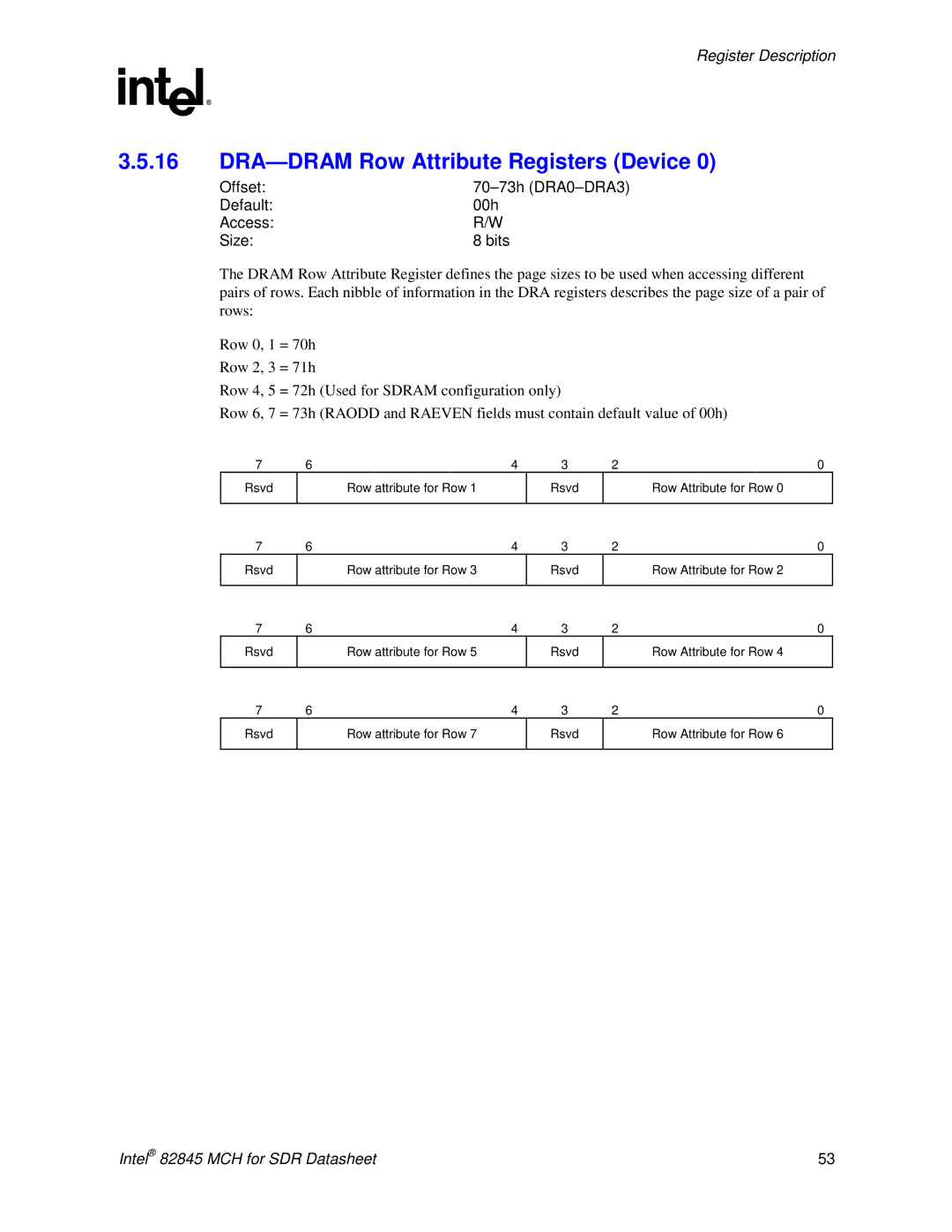

3.5.16DRA—DRAM Row Attribute Registers (Device 0)

Offset: |

|

Default: | 00h |

Access: | R/W |

Size: | 8 bits |

The DRAM Row Attribute Register defines the page sizes to be used when accessing different pairs of rows. Each nibble of information in the DRA registers describes the page size of a pair of rows:

Row 0, 1 = 70h

Row 2, 3 = 71h

Row 4, 5 = 72h (Used for SDRAM configuration only)

Row 6, 7 = 73h (RAODD and RAEVEN fields must contain default value of 00h)

7 | 6 | 4 | 3 | 2 | 0 |

Rsvd | Row attribute for Row 1 |

| Rsvd |

| Row Attribute for Row 0 |

|

|

|

|

|

|

7 | 6 | 4 | 3 | 2 | 0 |

Rsvd | Row attribute for Row 3 |

| Rsvd |

| Row Attribute for Row 2 |

|

|

|

|

|

|

7 | 6 | 4 | 3 | 2 | 0 |

Rsvd | Row attribute for Row 5 |

| Rsvd |

| Row Attribute for Row 4 |

|

|

|

|

|

|

7 | 6 | 4 | 3 | 2 | 0 |

Rsvd | Row attribute for Row 7 |

| Rsvd |

| Row Attribute for Row 6 |

|

|

|

|

|

|

Intel® 82845 MCH for SDR Datasheet | 53 |