Signal Description

R

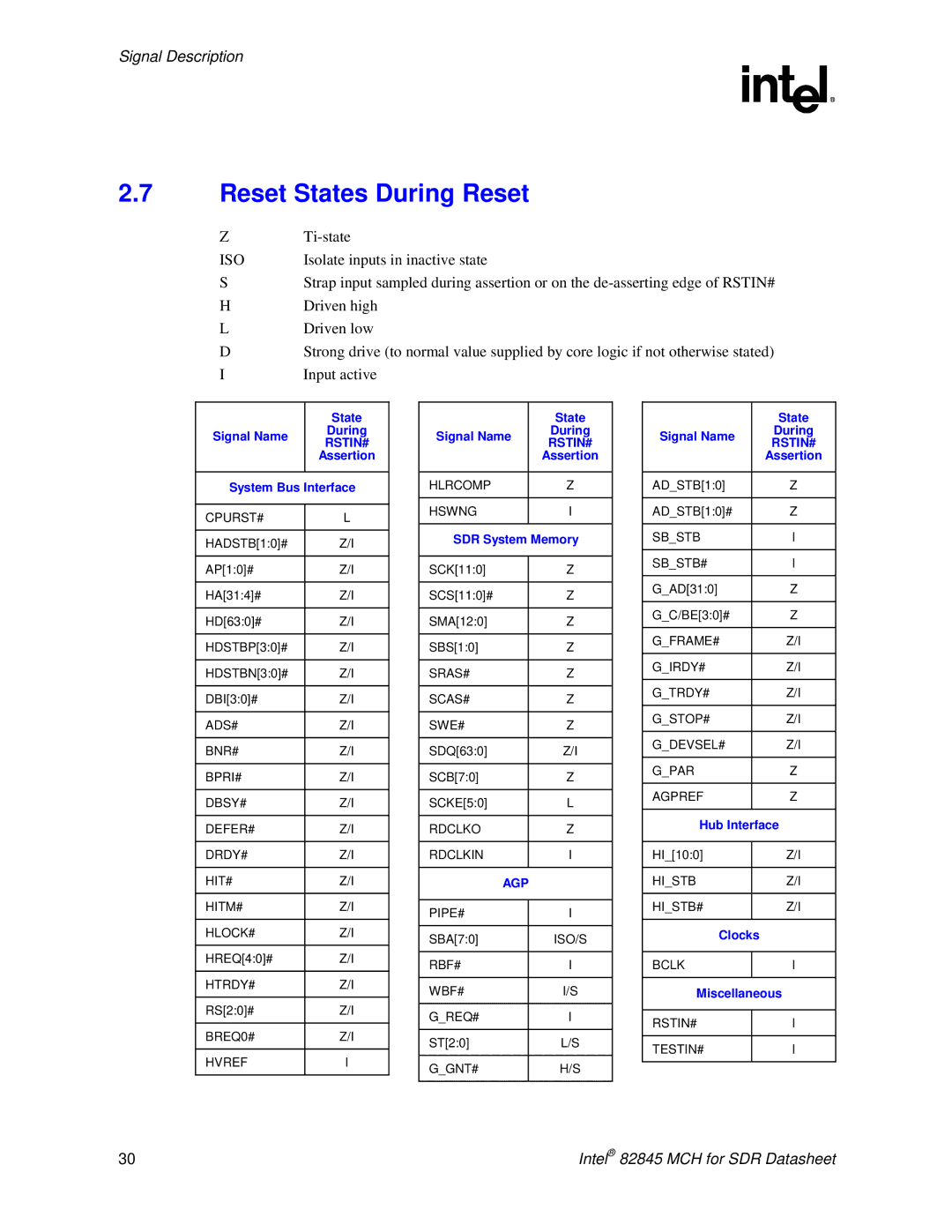

2.7Reset States During Reset

Z | |

ISO | Isolate inputs in inactive state |

S | Strap input sampled during assertion or on the |

H | Driven high |

L | Driven low |

D | Strong drive (to normal value supplied by core logic if not otherwise stated) |

I | Input active |

| State |

Signal Name | During |

RSTIN# | |

| Assertion |

|

|

System Bus Interface | |

|

|

CPURST# | L |

|

|

HADSTB[1:0]# | Z/I |

|

|

AP[1:0]# | Z/I |

|

|

HA[31:4]# | Z/I |

|

|

HD[63:0]# | Z/I |

|

|

HDSTBP[3:0]# | Z/I |

|

|

HDSTBN[3:0]# | Z/I |

|

|

DBI[3:0]# | Z/I |

|

|

ADS# | Z/I |

|

|

BNR# | Z/I |

|

|

BPRI# | Z/I |

|

|

DBSY# | Z/I |

|

|

DEFER# | Z/I |

|

|

DRDY# | Z/I |

|

|

HIT# | Z/I |

|

|

HITM# | Z/I |

|

|

HLOCK# | Z/I |

|

|

HREQ[4:0]# | Z/I |

|

|

HTRDY# | Z/I |

|

|

RS[2:0]# | Z/I |

|

|

BREQ0# | Z/I |

|

|

HVREF | I |

|

|

| State |

Signal Name | During |

RSTIN# | |

| Assertion |

|

|

HLRCOMP | Z |

|

|

HSWNG | I |

|

|

SDR System Memory | |

|

|

SCK[11:0] | Z |

|

|

SCS[11:0]# | Z |

|

|

SMA[12:0] | Z |

|

|

SBS[1:0] | Z |

|

|

SRAS# | Z |

|

|

SCAS# | Z |

|

|

SWE# | Z |

|

|

SDQ[63:0] | Z/I |

|

|

SCB[7:0] | Z |

|

|

SCKE[5:0] | L |

|

|

RDCLKO | Z |

|

|

RDCLKIN | I |

|

|

AGP |

|

|

|

PIPE# | I |

|

|

SBA[7:0] | ISO/S |

|

|

RBF# | I |

|

|

WBF# | I/S |

|

|

G_REQ# | I |

|

|

ST[2:0] | L/S |

|

|

G_GNT# | H/S |

|

|

|

| State |

Signal Name |

| During |

| RSTIN# | |

|

| Assertion |

|

|

|

AD_STB[1:0] |

| Z |

|

|

|

AD_STB[1:0]# |

| Z |

|

|

|

SB_STB |

| I |

|

|

|

SB_STB# |

| I |

|

|

|

G_AD[31:0] |

| Z |

|

|

|

G_C/BE[3:0]# |

| Z |

|

|

|

G_FRAME# |

| Z/I |

|

|

|

G_IRDY# |

| Z/I |

|

|

|

G_TRDY# |

| Z/I |

|

|

|

G_STOP# |

| Z/I |

|

|

|

G_DEVSEL# |

| Z/I |

|

|

|

G_PAR |

| Z |

|

|

|

AGPREF |

| Z |

|

| |

Hub Interface | ||

|

|

|

HI_[10:0] |

| Z/I |

|

|

|

HI_STB |

| Z/I |

|

|

|

HI_STB# |

| Z/I |

|

|

|

Clocks |

| |

|

| |

BCLK |

| I |

|

| |

Miscellaneous | ||

|

| |

RSTIN# |

| I |

|

|

|

TESTIN# |

| I |

|

|

|

30 | Intel® 82845 MCH for SDR Datasheet |