Testability

R

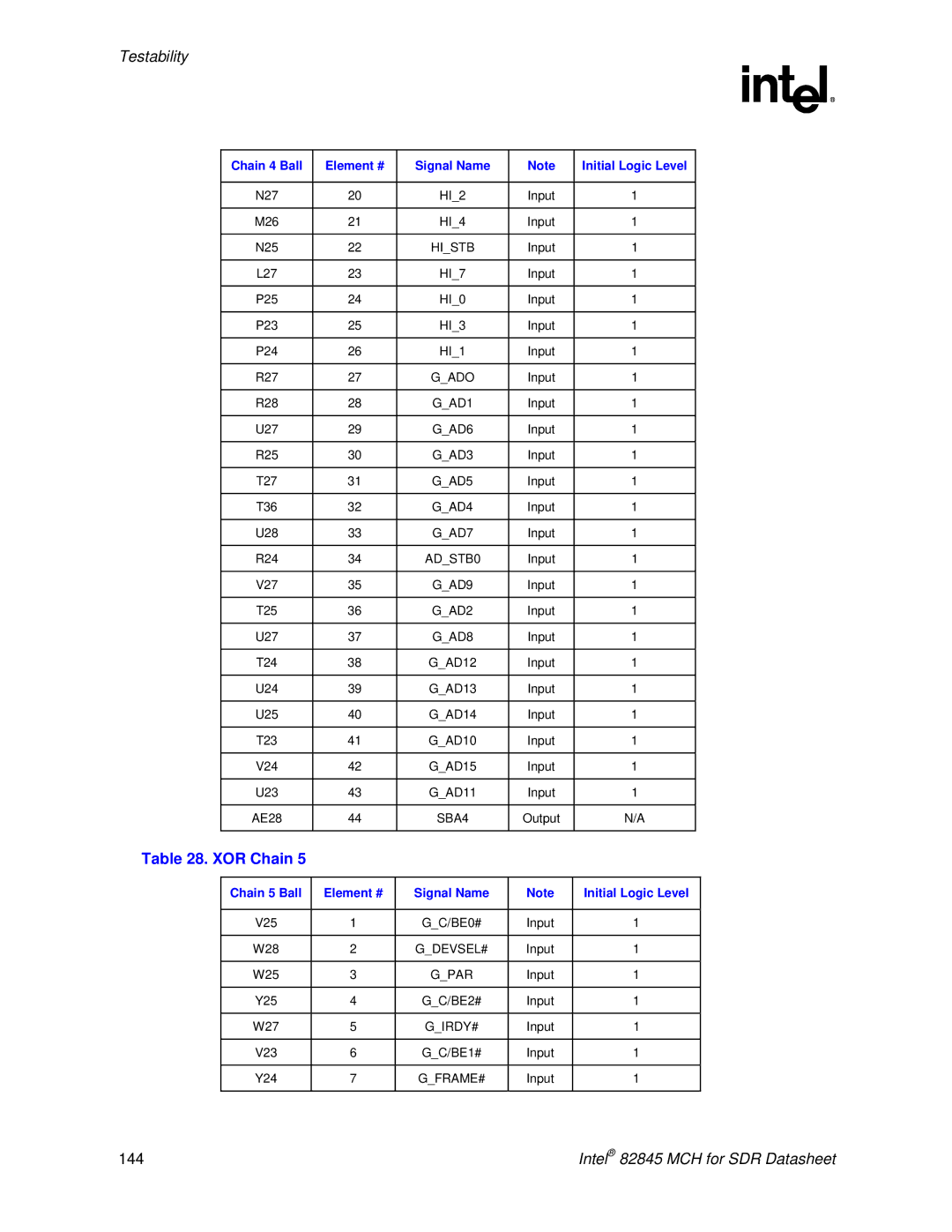

Chain 4 Ball | Element # | Signal Name | Note | Initial Logic Level |

|

|

|

|

|

N27 | 20 | HI_2 | Input | 1 |

|

|

|

|

|

M26 | 21 | HI_4 | Input | 1 |

|

|

|

|

|

N25 | 22 | HI_STB | Input | 1 |

|

|

|

|

|

L27 | 23 | HI_7 | Input | 1 |

|

|

|

|

|

P25 | 24 | HI_0 | Input | 1 |

|

|

|

|

|

P23 | 25 | HI_3 | Input | 1 |

|

|

|

|

|

P24 | 26 | HI_1 | Input | 1 |

|

|

|

|

|

R27 | 27 | G_ADO | Input | 1 |

|

|

|

|

|

R28 | 28 | G_AD1 | Input | 1 |

|

|

|

|

|

U27 | 29 | G_AD6 | Input | 1 |

|

|

|

|

|

R25 | 30 | G_AD3 | Input | 1 |

|

|

|

|

|

T27 | 31 | G_AD5 | Input | 1 |

|

|

|

|

|

T36 | 32 | G_AD4 | Input | 1 |

|

|

|

|

|

U28 | 33 | G_AD7 | Input | 1 |

|

|

|

|

|

R24 | 34 | AD_STB0 | Input | 1 |

|

|

|

|

|

V27 | 35 | G_AD9 | Input | 1 |

|

|

|

|

|

T25 | 36 | G_AD2 | Input | 1 |

|

|

|

|

|

U27 | 37 | G_AD8 | Input | 1 |

|

|

|

|

|

T24 | 38 | G_AD12 | Input | 1 |

|

|

|

|

|

U24 | 39 | G_AD13 | Input | 1 |

|

|

|

|

|

U25 | 40 | G_AD14 | Input | 1 |

|

|

|

|

|

T23 | 41 | G_AD10 | Input | 1 |

|

|

|

|

|

V24 | 42 | G_AD15 | Input | 1 |

|

|

|

|

|

U23 | 43 | G_AD11 | Input | 1 |

|

|

|

|

|

AE28 | 44 | SBA4 | Output | N/A |

|

|

|

|

|

Table 28. XOR Chain 5

Chain 5 Ball | Element # | Signal Name | Note | Initial Logic Level |

|

|

|

|

|

V25 | 1 | G_C/BE0# | Input | 1 |

|

|

|

|

|

W28 | 2 | G_DEVSEL# | Input | 1 |

|

|

|

|

|

W25 | 3 | G_PAR | Input | 1 |

|

|

|

|

|

Y25 | 4 | G_C/BE2# | Input | 1 |

|

|

|

|

|

W27 | 5 | G_IRDY# | Input | 1 |

|

|

|

|

|

V23 | 6 | G_C/BE1# | Input | 1 |

|

|

|

|

|

Y24 | 7 | G_FRAME# | Input | 1 |

|

|

|

|

|

144 | Intel® 82845 MCH for SDR Datasheet |