Register Description

R

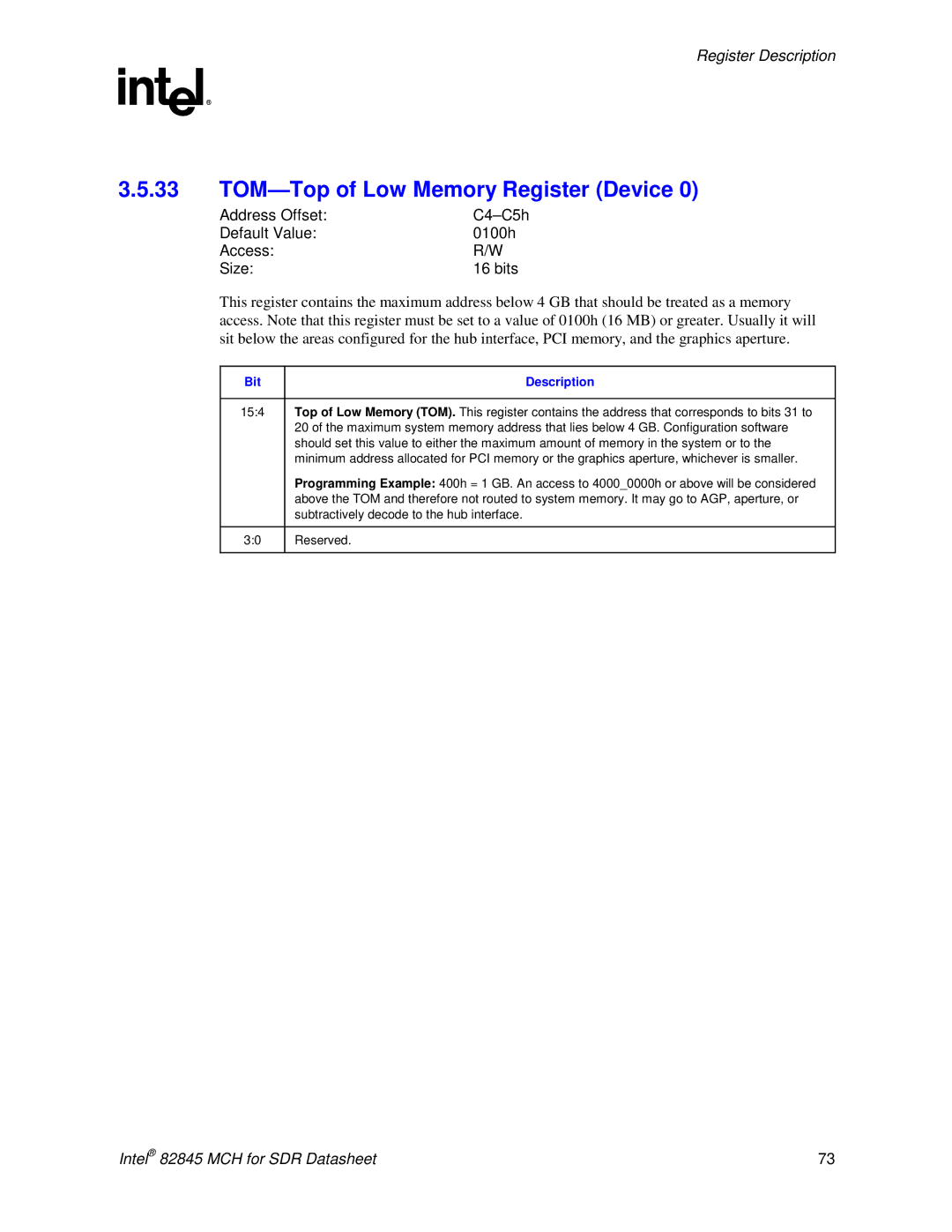

3.5.33TOM—Top of Low Memory Register (Device 0)

Address Offset: |

|

Default Value: | 0100h |

Access: | R/W |

Size: | 16 bits |

This register contains the maximum address below 4 GB that should be treated as a memory access. Note that this register must be set to a value of 0100h (16 MB) or greater. Usually it will sit below the areas configured for the hub interface, PCI memory, and the graphics aperture.

Bit | Description |

|

|

15:4 | Top of Low Memory (TOM). This register contains the address that corresponds to bits 31 to |

| 20 of the maximum system memory address that lies below 4 GB. Configuration software |

| should set this value to either the maximum amount of memory in the system or to the |

| minimum address allocated for PCI memory or the graphics aperture, whichever is smaller. |

| Programming Example: 400h = 1 GB. An access to 4000_0000h or above will be considered |

| above the TOM and therefore not routed to system memory. It may go to AGP, aperture, or |

| subtractively decode to the hub interface. |

|

|

3:0 | Reserved. |

|

|

Intel® 82845 MCH for SDR Datasheet | 73 |