Signal Description

R

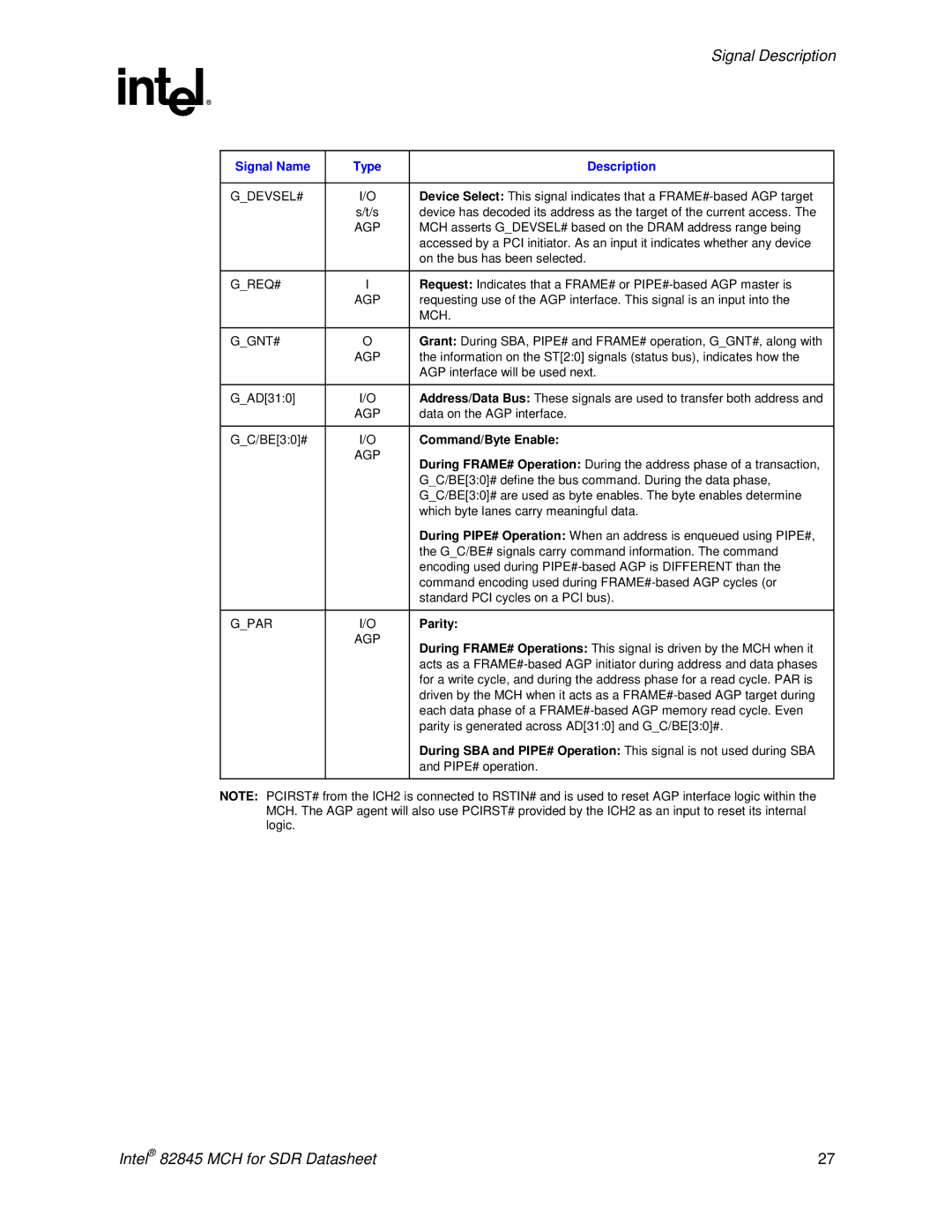

Signal Name | Type | Description |

|

|

|

G_DEVSEL# | I/O | Device Select: This signal indicates that a |

| s/t/s | device has decoded its address as the target of the current access. The |

| AGP | MCH asserts G_DEVSEL# based on the DRAM address range being |

|

| accessed by a PCI initiator. As an input it indicates whether any device |

|

| on the bus has been selected. |

|

|

|

G_REQ# | I | Request: Indicates that a FRAME# or |

| AGP | requesting use of the AGP interface. This signal is an input into the |

|

| MCH. |

|

|

|

G_GNT# | O | Grant: During SBA, PIPE# and FRAME# operation, G_GNT#, along with |

| AGP | the information on the ST[2:0] signals (status bus), indicates how the |

|

| AGP interface will be used next. |

|

|

|

G_AD[31:0] | I/O | Address/Data Bus: These signals are used to transfer both address and |

| AGP | data on the AGP interface. |

|

|

|

G_C/BE[3:0]# | I/O | Command/Byte Enable: |

| AGP | During FRAME# Operation: During the address phase of a transaction, |

|

| |

|

| G_C/BE[3:0]# define the bus command. During the data phase, |

|

| G_C/BE[3:0]# are used as byte enables. The byte enables determine |

|

| which byte lanes carry meaningful data. |

|

| During PIPE# Operation: When an address is enqueued using PIPE#, |

|

| the G_C/BE# signals carry command information. The command |

|

| encoding used during |

|

| command encoding used during |

|

| standard PCI cycles on a PCI bus). |

|

|

|

G_PAR | I/O | Parity: |

| AGP | During FRAME# Operations: This signal is driven by the MCH when it |

|

| |

|

| acts as a |

|

| for a write cycle, and during the address phase for a read cycle. PAR is |

|

| driven by the MCH when it acts as a |

|

| each data phase of a |

|

| parity is generated across AD[31:0] and G_C/BE[3:0]#. |

|

| During SBA and PIPE# Operation: This signal is not used during SBA |

|

| and PIPE# operation. |

|

|

|

NOTE: PCIRST# from the ICH2 is connected to RSTIN# and is used to reset AGP interface logic within the MCH. The AGP agent will also use PCIRST# provided by the ICH2 as an input to reset its internal logic.

Intel® 82845 MCH for SDR Datasheet | 27 |