System Address Map

R

4.3.1SMM Space Definition

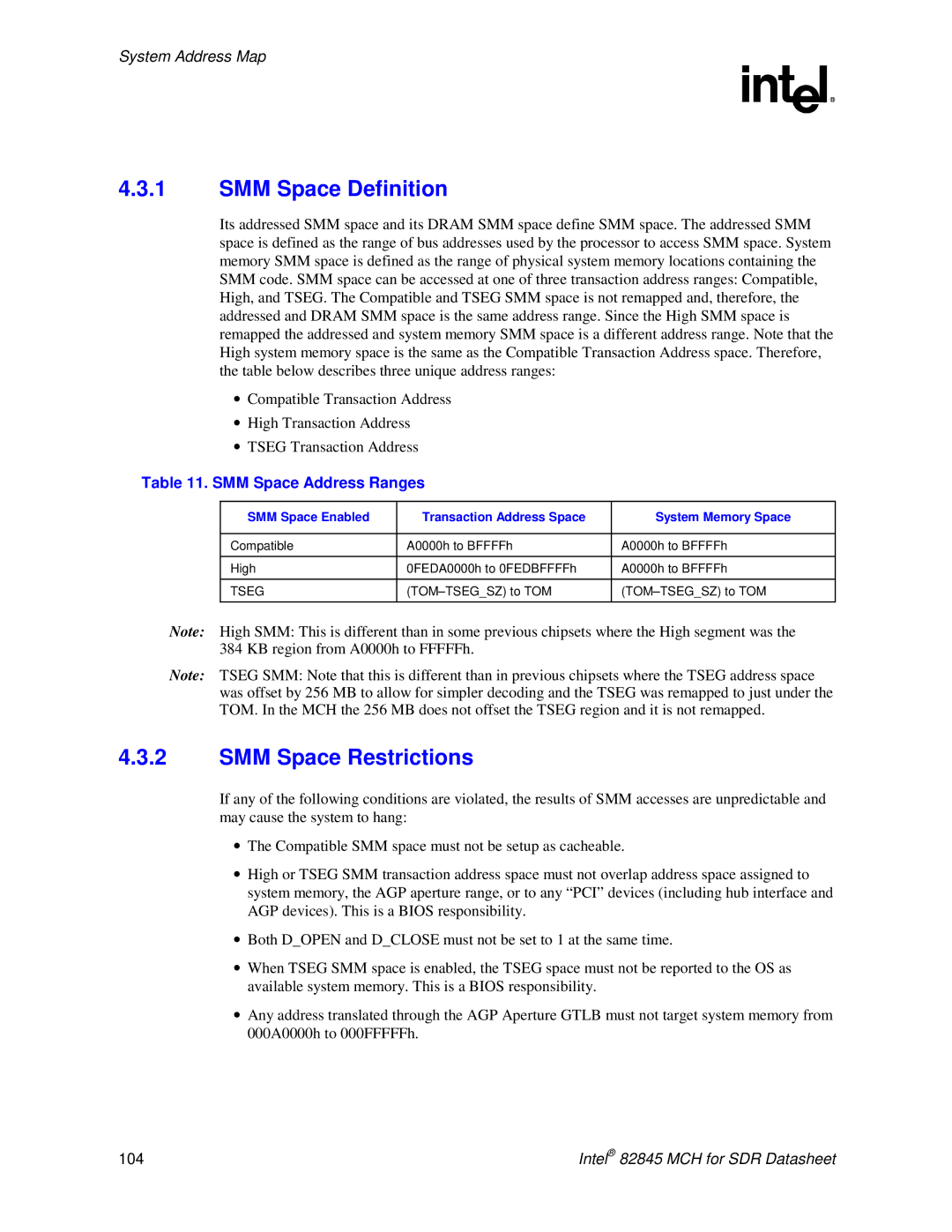

Its addressed SMM space and its DRAM SMM space define SMM space. The addressed SMM space is defined as the range of bus addresses used by the processor to access SMM space. System memory SMM space is defined as the range of physical system memory locations containing the SMM code. SMM space can be accessed at one of three transaction address ranges: Compatible, High, and TSEG. The Compatible and TSEG SMM space is not remapped and, therefore, the addressed and DRAM SMM space is the same address range. Since the High SMM space is remapped the addressed and system memory SMM space is a different address range. Note that the High system memory space is the same as the Compatible Transaction Address space. Therefore, the table below describes three unique address ranges:

•Compatible Transaction Address

•High Transaction Address

•TSEG Transaction Address

Table 11. SMM Space Address Ranges

SMM Space Enabled | Transaction Address Space | System Memory Space |

|

|

|

Compatible | A0000h to BFFFFh | A0000h to BFFFFh |

High | 0FEDA0000h to 0FEDBFFFFh | A0000h to BFFFFh |

|

|

|

TSEG |

Note: High SMM: This is different than in some previous chipsets where the High segment was the 384 KB region from A0000h to FFFFFh.

Note: TSEG SMM: Note that this is different than in previous chipsets where the TSEG address space was offset by 256 MB to allow for simpler decoding and the TSEG was remapped to just under the TOM. In the MCH the 256 MB does not offset the TSEG region and it is not remapped.

4.3.2SMM Space Restrictions

If any of the following conditions are violated, the results of SMM accesses are unpredictable and may cause the system to hang:

•The Compatible SMM space must not be setup as cacheable.

•High or TSEG SMM transaction address space must not overlap address space assigned to system memory, the AGP aperture range, or to any “PCI” devices (including hub interface and AGP devices). This is a BIOS responsibility.

•Both D_OPEN and D_CLOSE must not be set to 1 at the same time.

•When TSEG SMM space is enabled, the TSEG space must not be reported to the OS as available system memory. This is a BIOS responsibility.

•Any address translated through the AGP Aperture GTLB must not target system memory from 000A0000h to 000FFFFFh.

104 | Intel® 82845 MCH for SDR Datasheet |