Register Description

R

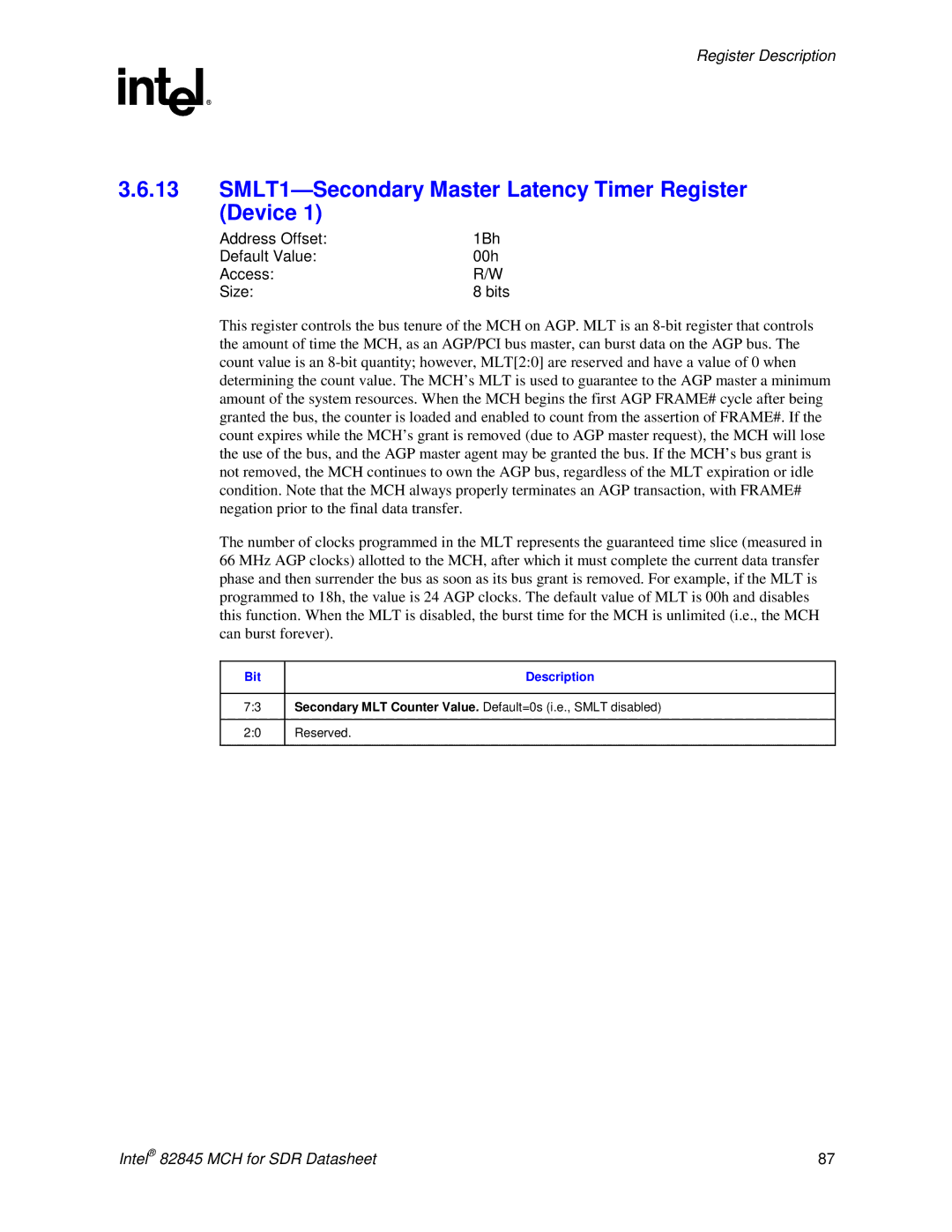

3.6.13SMLT1—Secondary Master Latency Timer Register (Device 1)

Address Offset: | 1Bh |

Default Value: | 00h |

Access: | R/W |

Size: | 8 bits |

This register controls the bus tenure of the MCH on AGP. MLT is an

The number of clocks programmed in the MLT represents the guaranteed time slice (measured in 66 MHz AGP clocks) allotted to the MCH, after which it must complete the current data transfer phase and then surrender the bus as soon as its bus grant is removed. For example, if the MLT is programmed to 18h, the value is 24 AGP clocks. The default value of MLT is 00h and disables this function. When the MLT is disabled, the burst time for the MCH is unlimited (i.e., the MCH can burst forever).

Bit | Description |

|

|

7:3 | Secondary MLT Counter Value. Default=0s (i.e., SMLT disabled) |

|

|

2:0 | Reserved. |

|

|

Intel® 82845 MCH for SDR Datasheet | 87 |