Signal Description

R

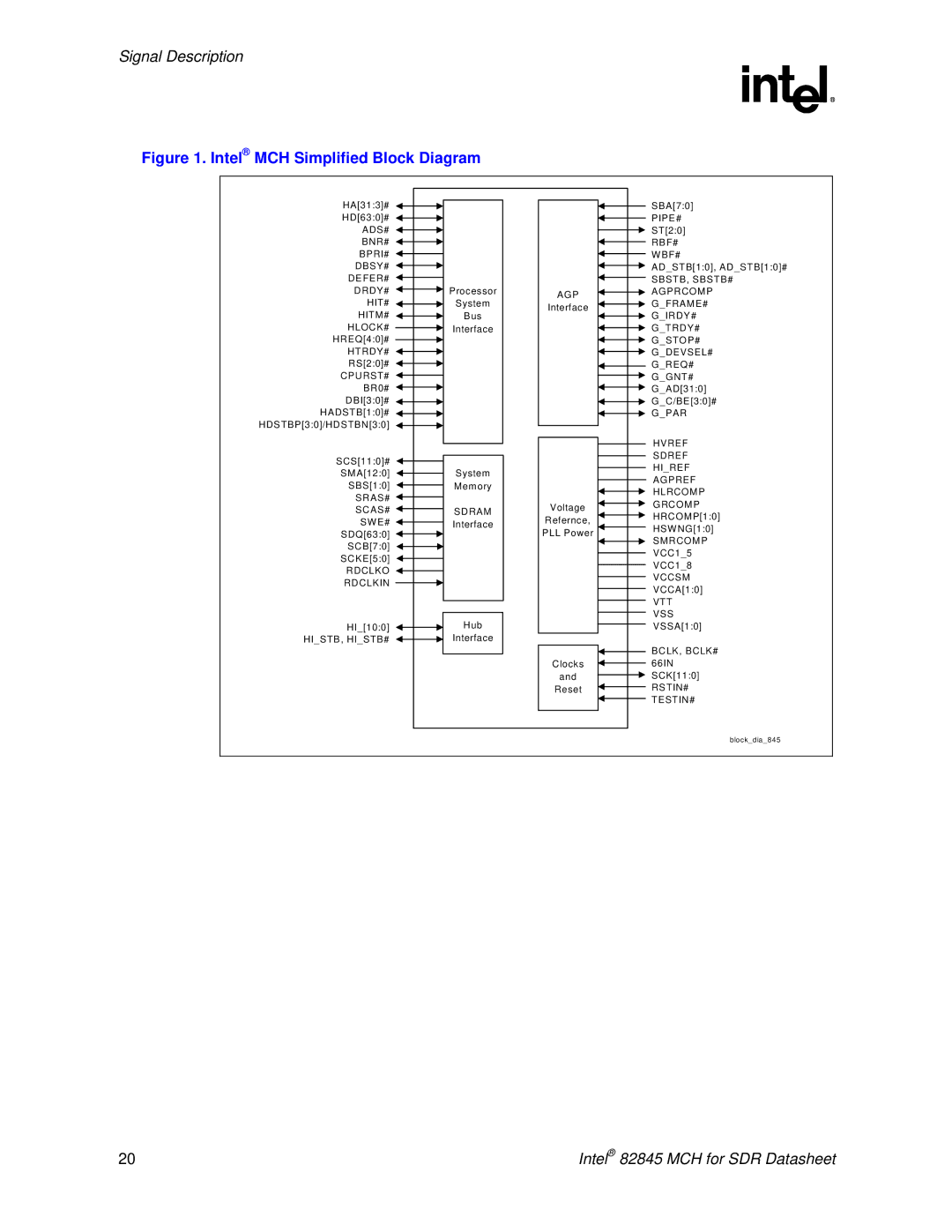

Figure 1. Intel® MCH Simplified Block Diagram

HA[31:3]# |

|

HD[63:0]# |

|

ADS# |

|

BNR# |

|

BPRI# |

|

DBSY# |

|

DEFER# |

|

DRDY# | Processor |

HIT# | System |

HITM# | Bus |

HLOCK# | Interface |

HREQ[4:0]# |

|

HTRDY# |

|

RS[2:0]# |

|

CPURST# |

|

BR0# |

|

DBI[3:0]# |

|

HADSTB[1:0]# |

|

HDSTBP[3:0]/HDSTBN[3:0] |

|

SCS[11:0]# |

|

SM A[12:0] | System |

SBS[1:0] | Memory |

SRAS# |

|

SCAS# | SDRAM |

SW E# | Interface |

SDQ[63:0] |

|

SCB[7:0] |

|

SCKE[5:0] |

|

RDCLKO |

|

RDCLKIN |

|

HI_[10:0] | Hub |

HI_STB, HI_STB# | Interface |

AGP |

Interface |

Voltage |

Refernce, |

PLL Power |

Clocks |

and |

Reset |

SBA[7:0] PIPE# ST[2:0] RBF# WBF#

AD_STB[1:0], AD_STB[1:0]#

SBSTB, SBSTB# AGPRCOMP

G_FRAME# G_IRDY# G_TRDY# G_STOP# G_DEVSEL# G_REQ#

G_GNT#

G_AD[31:0] G_C/BE[3:0]# G_PAR

HVREF

SDREF

HI_REF

AGPREF

HLRCOMP

GRCOMP

HRCOMP[1:0]

HSWNG[1:0]

SMRCOMP

VCC1_5

VCC1_8

VCCSM

VCCA[1:0]

VTT

VSS

VSSA[1:0]

BCLK, BCLK# 66IN SCK[11:0]

RSTIN#

TESTIN#

block_dia_845

20 | Intel® 82845 MCH for SDR Datasheet |