R

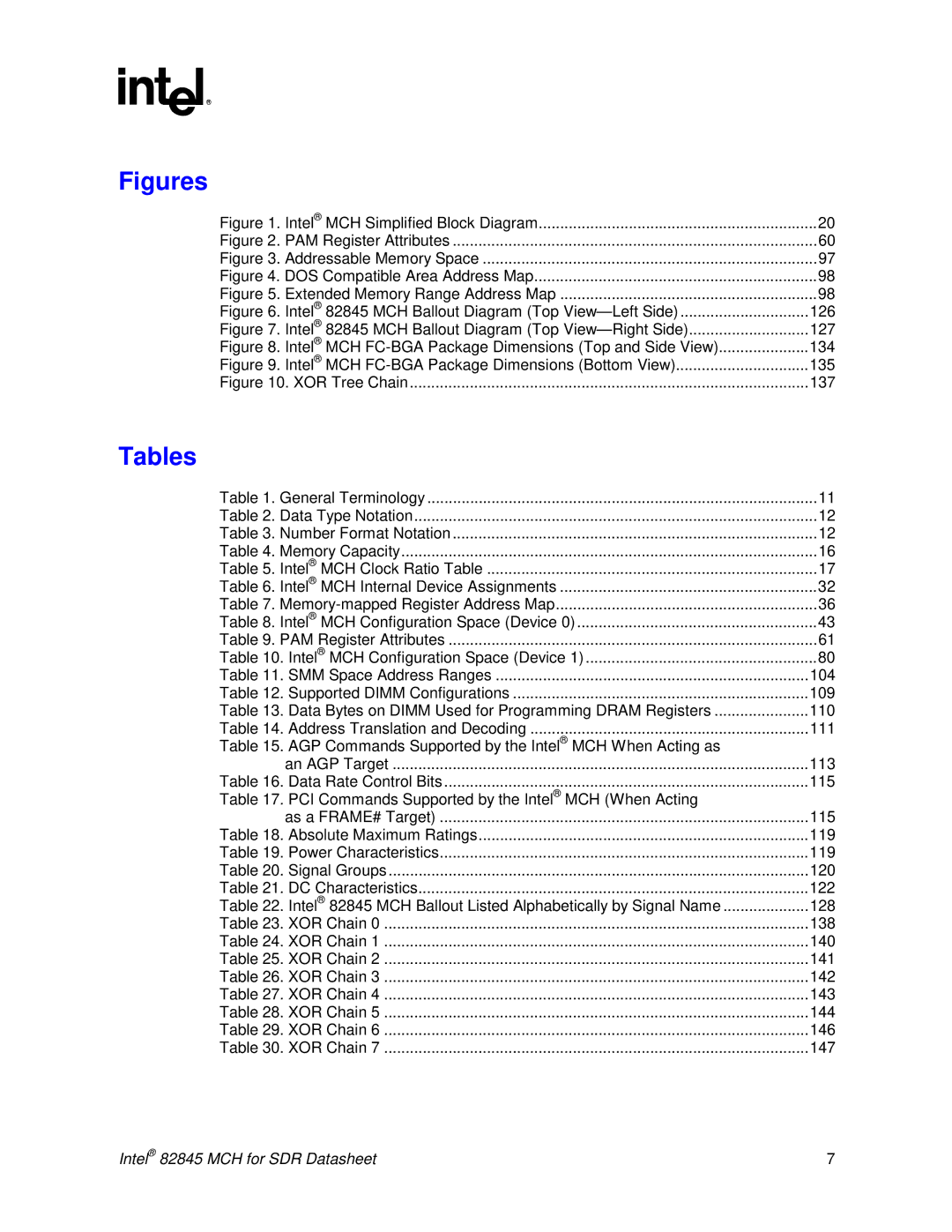

Figures

Figure 1. Intel® MCH Simplified Block Diagram | 20 | |

Figure 2. PAM Register Attributes | 60 | |

Figure 3. Addressable Memory Space | 97 | |

Figure 4. DOS Compatible Area Address Map | 98 | |

Figure 5. Extended Memory Range Address Map | 98 | |

Figure 6. | Intel® 82845 MCH Ballout Diagram (Top | 126 |

Figure 7. | Intel® 82845 MCH Ballout Diagram (Top | 127 |

Figure 8. | Intel® MCH | 134 |

Figure 9. | Intel® MCH | 135 |

Figure 10. XOR Tree Chain | 137 | |

Tables

Table 1. General Terminology | 11 |

Table 2. Data Type Notation | 12 |

Table 3. Number Format Notation | 12 |

Table 4. Memory Capacity | 16 |

Table 5. Intel® MCH Clock Ratio Table | 17 |

Table 6. Intel® MCH Internal Device Assignments | 32 |

Table 7. | 36 |

Table 8. Intel® MCH Configuration Space (Device 0) | 43 |

Table 9. PAM Register Attributes | 61 |

Table 10. Intel® MCH Configuration Space (Device 1) | 80 |

Table 11. SMM Space Address Ranges | 104 |

Table 12. Supported DIMM Configurations | 109 |

Table 13. Data Bytes on DIMM Used for Programming DRAM Registers | 110 |

Table 14. Address Translation and Decoding | 111 |

Table 15. AGP Commands Supported by the Intel® MCH When Acting as |

|

an AGP Target | 113 |

Table 16. Data Rate Control Bits | 115 |

Table 17. PCI Commands Supported by the Intel® MCH (When Acting |

|

as a FRAME# Target) | 115 |

Table 18. Absolute Maximum Ratings | 119 |

Table 19. Power Characteristics | 119 |

Table 20. Signal Groups | 120 |

Table 21. DC Characteristics | 122 |

Table 22. Intel® 82845 MCH Ballout Listed Alphabetically by Signal Name | 128 |

Table 23. XOR Chain 0 | 138 |

Table 24. XOR Chain 1 | 140 |

Table 25. XOR Chain 2 | 141 |

Table 26. XOR Chain 3 | 142 |

Table 27. XOR Chain 4 | 143 |

Table 28. XOR Chain 5 | 144 |

Table 29. XOR Chain 6 | 146 |

Table 30. XOR Chain 7 | 147 |

Intel® 82845 MCH for SDR Datasheet | 7 |