Register Description

R

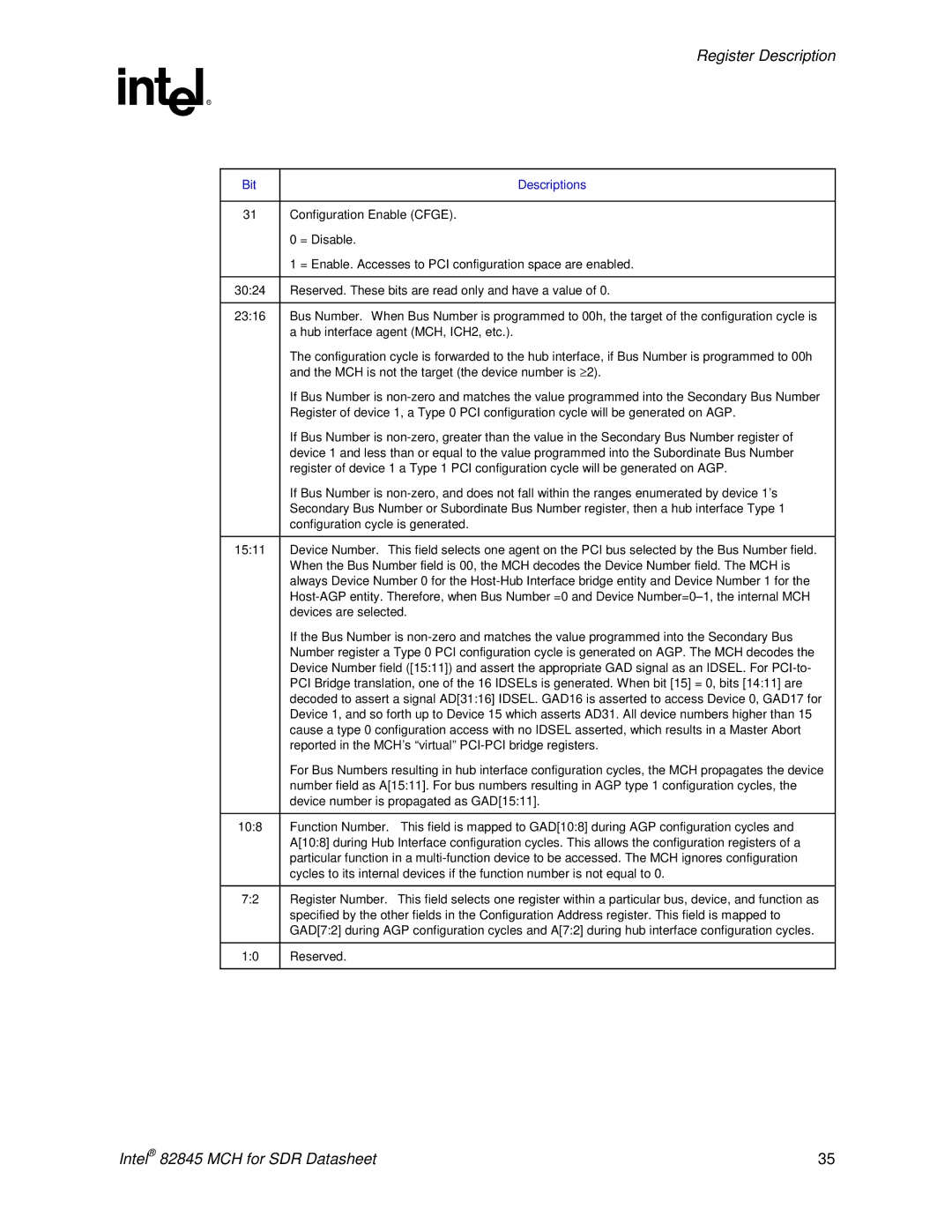

Bit | Descriptions |

|

|

31 | Configuration Enable (CFGE). |

| 0 = Disable. |

| 1 = Enable. Accesses to PCI configuration space are enabled. |

|

|

30:24 | Reserved. These bits are read only and have a value of 0. |

|

|

23:16 | Bus Number. When Bus Number is programmed to 00h, the target of the configuration cycle is |

| a hub interface agent (MCH, ICH2, etc.). |

| The configuration cycle is forwarded to the hub interface, if Bus Number is programmed to 00h |

| and the MCH is not the target (the device number is ≥ 2). |

| If Bus Number is |

| Register of device 1, a Type 0 PCI configuration cycle will be generated on AGP. |

| If Bus Number is |

| device 1 and less than or equal to the value programmed into the Subordinate Bus Number |

| register of device 1 a Type 1 PCI configuration cycle will be generated on AGP. |

| If Bus Number is |

| Secondary Bus Number or Subordinate Bus Number register, then a hub interface Type 1 |

| configuration cycle is generated. |

|

|

15:11 | Device Number. This field selects one agent on the PCI bus selected by the Bus Number field. |

| When the Bus Number field is 00, the MCH decodes the Device Number field. The MCH is |

| always Device Number 0 for the |

| |

| devices are selected. |

| If the Bus Number is |

| Number register a Type 0 PCI configuration cycle is generated on AGP. The MCH decodes the |

| Device Number field ([15:11]) and assert the appropriate GAD signal as an IDSEL. For |

| PCI Bridge translation, one of the 16 IDSELs is generated. When bit [15] = 0, bits [14:11] are |

| decoded to assert a signal AD[31:16] IDSEL. GAD16 is asserted to access Device 0, GAD17 for |

| Device 1, and so forth up to Device 15 which asserts AD31. All device numbers higher than 15 |

| cause a type 0 configuration access with no IDSEL asserted, which results in a Master Abort |

| reported in the MCH’s “virtual” |

| For Bus Numbers resulting in hub interface configuration cycles, the MCH propagates the device |

| number field as A[15:11]. For bus numbers resulting in AGP type 1 configuration cycles, the |

| device number is propagated as GAD[15:11]. |

|

|

10:8 | Function Number. This field is mapped to GAD[10:8] during AGP configuration cycles and |

| A[10:8] during Hub Interface configuration cycles. This allows the configuration registers of a |

| particular function in a |

| cycles to its internal devices if the function number is not equal to 0. |

|

|

7:2 | Register Number. This field selects one register within a particular bus, device, and function as |

| specified by the other fields in the Configuration Address register. This field is mapped to |

| GAD[7:2] during AGP configuration cycles and A[7:2] during hub interface configuration cycles. |

|

|

1:0 | Reserved. |

|

|

Intel® 82845 MCH for SDR Datasheet | 35 |