R

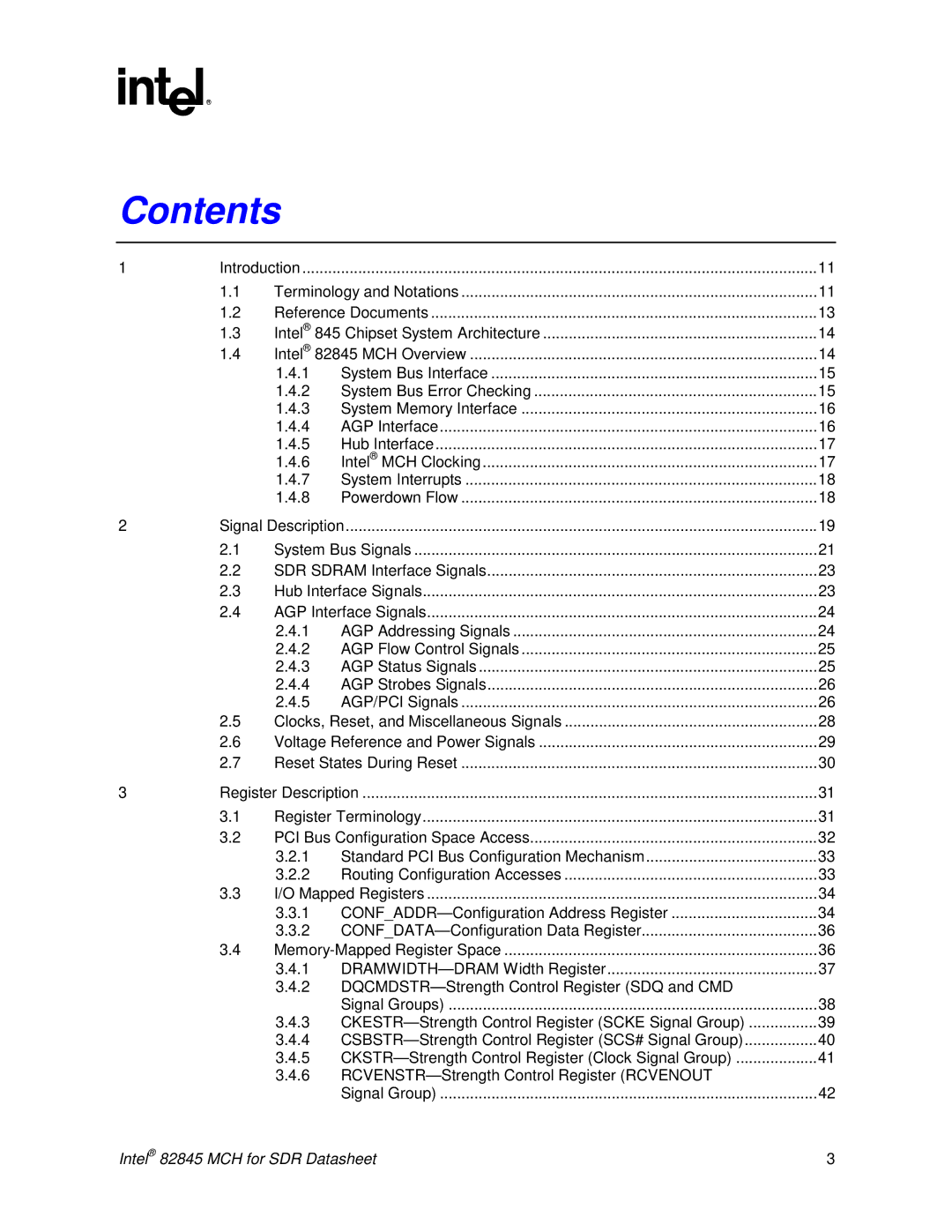

Contents

1 | Introduction | 11 | ||

| 1.1 | Terminology and Notations | 11 | |

| 1.2 | Reference Documents | 13 | |

| 1.3 | Intel® 845 Chipset System Architecture | 14 | |

| 1.4 | Intel® 82845 MCH Overview | 14 | |

|

| 1.4.1 | System Bus Interface | 15 |

|

| 1.4.2 | System Bus Error Checking | 15 |

|

| 1.4.3 | System Memory Interface | 16 |

|

| 1.4.4 | AGP Interface | 16 |

|

| 1.4.5 | Hub Interface | 17 |

|

| 1.4.6 | Intel® MCH Clocking | 17 |

|

| 1.4.7 | System Interrupts | 18 |

|

| 1.4.8 | Powerdown Flow | 18 |

2 | Signal Description | 19 | ||

| 2.1 | System Bus Signals | 21 | |

| 2.2 | SDR SDRAM Interface Signals | 23 | |

| 2.3 | Hub Interface Signals | 23 | |

| 2.4 | AGP Interface Signals | 24 | |

|

| 2.4.1 | AGP Addressing Signals | 24 |

|

| 2.4.2 | AGP Flow Control Signals | 25 |

|

| 2.4.3 | AGP Status Signals | 25 |

|

| 2.4.4 | AGP Strobes Signals | 26 |

|

| 2.4.5 | AGP/PCI Signals | 26 |

| 2.5 | Clocks, Reset, and Miscellaneous Signals | 28 | |

| 2.6 | Voltage Reference and Power Signals | 29 | |

| 2.7 | Reset States During Reset | 30 | |

3 | Register Description | 31 | ||

| 3.1 | Register Terminology | 31 | |

| 3.2 | PCI Bus Configuration Space Access | 32 | |

|

| 3.2.1 | Standard PCI Bus Configuration Mechanism | 33 |

|

| 3.2.2 | Routing Configuration Accesses | 33 |

| 3.3 | I/O Mapped Registers | 34 | |

|

| 3.3.1 | 34 | |

|

| 3.3.2 | 36 | |

| 3.4 | 36 | ||

|

| 3.4.1 | 37 | |

|

| 3.4.2 |

| |

|

|

| Signal Groups) | 38 |

|

| 3.4.3 | 39 | |

|

| 3.4.4 | 40 | |

|

| 3.4.5 | 41 | |

|

| 3.4.6 |

| |

|

|

| Signal Group) | 42 |

Intel® 82845 MCH for SDR Datasheet | 3 | |||